## <u>Lecture – 8</u>

# Date: 05.09.2016

- CS Amplifier with Constant Current Source

- Current Steering Circuits

- CS Stage Followed by CG Stage

- Cascode as Current Source

- Cascode as Amplifier

$\bullet_{v_o(t)}$

# CS Amplifier with Constant Current Source

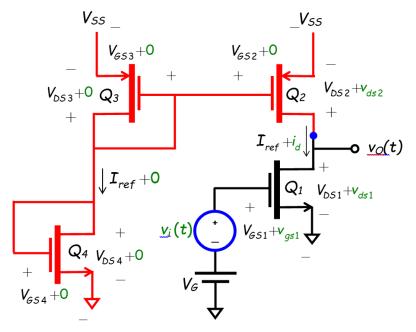

VGS3 -0vo(t)  $I_{ref}$  $v_i(t)$  $V_i(t)$ V<sub>G</sub> The important thing to realize when analyzing this circuit is that the gate-tosource voltage for transistors  $Q_2$ ,  $Q_3$ , and  $Q_4$  are **DC values**!

#### ??

Transistors  $Q_2$ ,  $Q_3$ , and  $Q_4$ form the **current mirror** that acts as the **current source**. Note that transistor  $Q_4$  is an **enhancement load**—it acts as the **resistor** in the current mirror circuit.

source resistance  $r_o$  of this current source  $\rightarrow$  requires the small-signal analysis  $\rightarrow$  there are four (count em') transistors in this circuit, determining the small-signal circuit must take forever!  $\rightarrow$  the answer is actually a NO.

A: In other words, the small signal voltages  $v_{as}$  for each transistor are equal to **zero**:

$v_{gs2} = v_{gs3} = v_{gs4} = 0$

## CS Amplifier with Constant Current Source (contd.)

**Q:** But doesn't the small-signal source  $v_i(t)$  create small-signal voltages and currents throughout the amplifier?

A: For **some** of the circuit yes, but for **most** of the circuit no!

Note that for transistor  $\mathbf{Q_1}$  there will be small-signal voltages  $v_{gs1}(t)$  and  $v_{ds1}(t)$ , along with  $i_{d1}(t)$ . Likewise for transistor  $\mathbf{Q_2}$ , a small-signal voltage  $v_{ds2}(t)$  and current  $i_{d2}(t)$  will occur.

But, for the remainder of the voltages and currents in this circuit (e.g.,  $V_{DS4}$ ,  $V_{GS2}$ ,  $I_{D3}$ ), the small-signal component is zero!

### CS Amplifier with Constant Current Source (contd.)

**Q:** But wait! **How** can there be a smallsignal **drain current**  $i_{d2}(t)$  through transistor Q<sub>2</sub>, without a corresponding small-signal  $v_{gs2}(t)$  gate-to-source voltage?

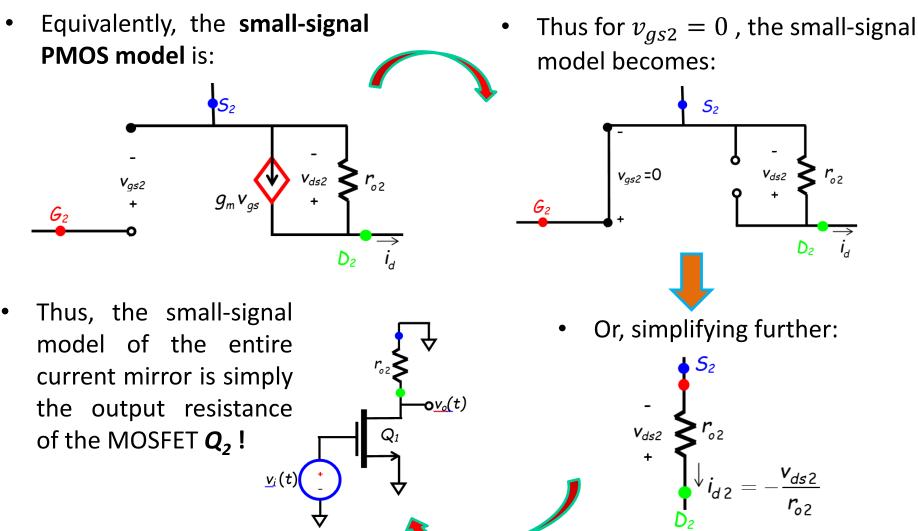

A: Transistor  $Q_2$  is **the** important device in this analysis.

- Note its gate-to-source voltage is a **DC** value (no small-signal component,  $v_{gs2}(t) = 0$  ), yet there **must** be (by KCL) a **small-signal** drain current!

- This is a case where we **must** consider the **MOSFET output resistance**  $r_{o2}$ . The small-signal  $i_{d2} = g_{m2} v_{gs2} - \frac{v_{ds2}}{r_{o2}}$ drain current for a PMOS device is:

Since  $v_{gs2} = 0$  , this equation **simplifies** to:  $i_{d2} =$

## CS Amplifier with Constant Current Source (contd.)

r<sub>02</sub>

## CS Amplifier with Constant Current Source (contd.)

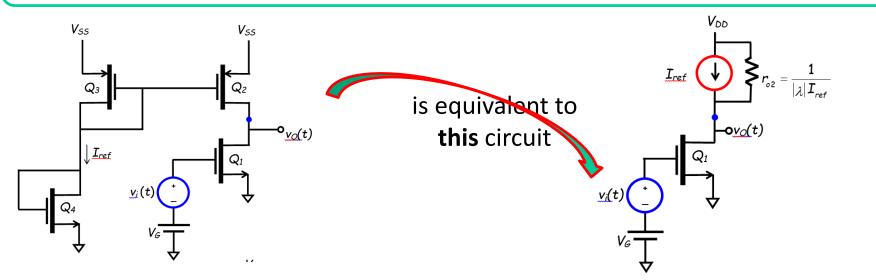

It is evident that the output resistance of the current mirror is simply equal to the output resistance of MOSFET  $Q_2$  !!!!

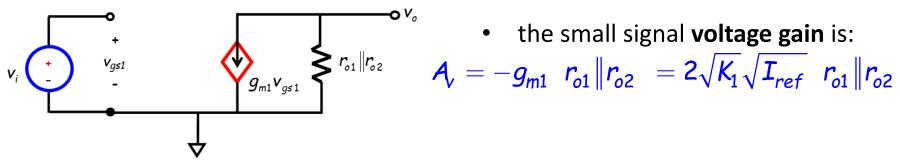

• The resulting small-signal circuit of this amp is:

## CS Amplifier with Constant Current Source (contd.)

- Note **this** result is **far different** (i.e., larger) than the result when using the **enhancement load** for  $R_D$ :

- However, we find that the **output** and **input** resistances of this amplifier are the **same** as  $R_i = \infty$ with the enhancement load:

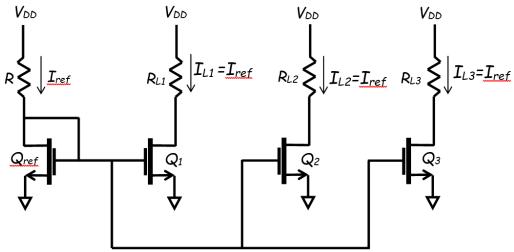

- A current mirror may consist of **many** MOSFET current sources!

This circuit is particularly useful in integrated circuit design, where **one** resistor *R* is used to make **multiple** current sources.

$\boldsymbol{R}_{o} = \boldsymbol{r}_{o1} \| \boldsymbol{r}_{o2}$

**Q:** What if we want to make the sources have **different** current values? Do we need to make **additional** current mirrors?

### **Current Steering Circuits**

- A: NO!!

- Recall that the current mirror simply ensures that the gate to source voltages of **each** transistor is **equal** to the gate to source  $V_{GS}^{ref} = V_{GS1} = V_{GS2} = V_{GS3} = \cdots$ voltage of the **reference**:

- Therefore, **if** each transistor is identical (i.e.,  $K_{ref} = K_1 = \cdots$ , and  $V^{ref}_T = V_{T1} = V_{T2} = \cdots$ ) then:

In other words, **if** each transistor  $Q_n$  is **identical** to  $Q_{ref}$ , then each current  $I_{Dn}$  will **equal** reference current  $I_{ref}$ .

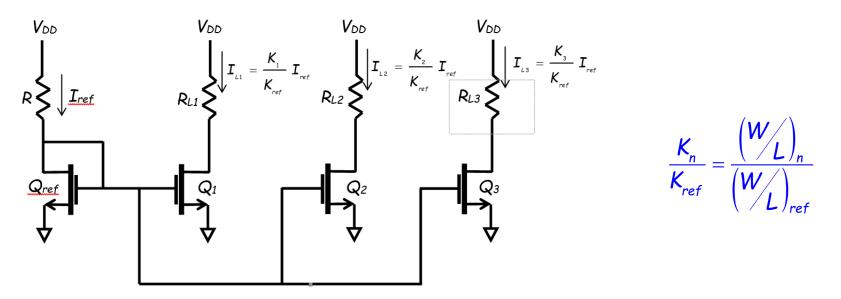

- **But,** consider what happens if the MOSFETS are not identical. Specifically, consider the case where  $K_n \neq K_{ref}$  (but  $V_{Tn} = (V_T)^{Ref}$ ).

- In such a scenario the drain current *I<sub>Dn</sub>*will now be:

- $\mathbf{I}_{Dn} = \mathbf{K}_{n} \left( \mathbf{V}_{GSn} \mathbf{V}_{Tn} \right)^{2} = \mathbf{K}_{n} \left( \mathbf{V}_{GS}^{ref} \mathbf{V}_{T}^{ref} \right)^{2}$  $= \mathbf{K}_{n} \left( \frac{\mathbf{I}_{ref}}{\mathbf{K}_{ref}} \right) = \left( \frac{\mathbf{K}_{n}}{\mathbf{K}_{ref}} \right) \mathbf{I}_{ref}$

- The drain current is a scaled value of *I<sub>ref</sub>* !

$\boldsymbol{I}_{ref} = \boldsymbol{K}_{ref} \left( \boldsymbol{V}_{GS}^{ref} - \boldsymbol{V}_{T}^{ref} \right)^{2}$

$=K_n\left(V_{GSn}-V_{Tn}\right)^2=I_{Dn}$

#### **Current Steering Circuits (contd.)**

For example, if  $K_1$  is twice that of  $K_{ref}$  (i.e.,  $K_1 = 2K_{ref}$ ), then  $I_{D1}$  will be twice as large as  $I_{ref}$  (i.e.,  $I_{D1} = 2I_{ref}$ ).

From the standpoint of integrated circuit design, we can change the value of K by modifying the MOSFET channel **width-tolength ratio** (W/L) for each transistor.

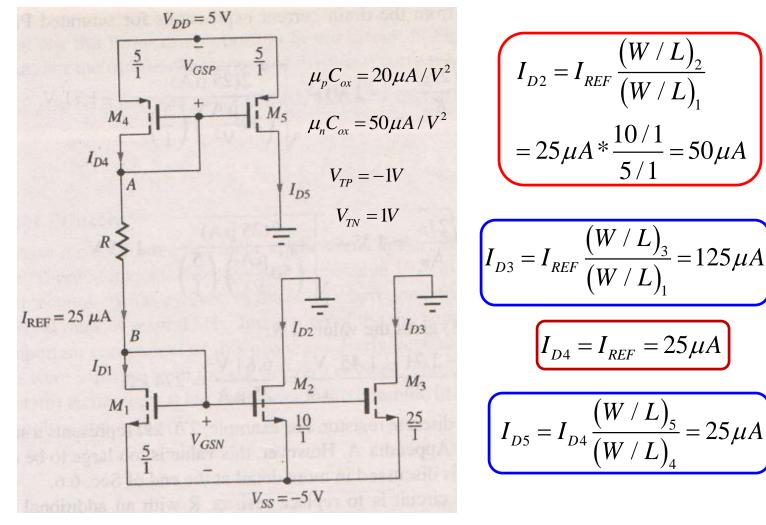

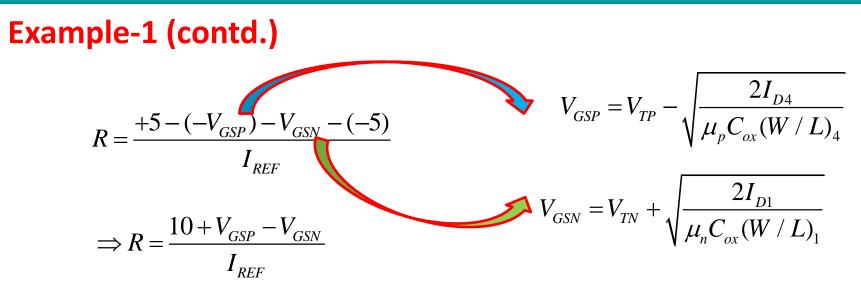

## **Example-1**

• Determine all the currents in the following and find the value of R

The resistor R can be replaced by an active load such as the PFET shown here → what will be its W/L?

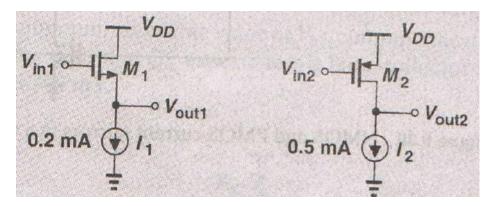

#### Example-2

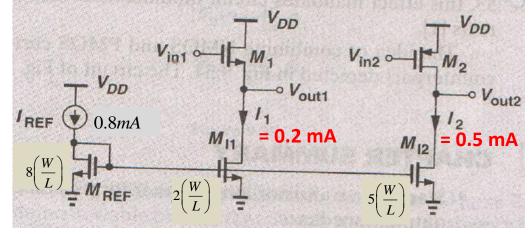

An integrated circuit employs the following CD and CS stages. Design an NMOS type current mirror that produces I<sub>1</sub> and I<sub>2</sub> from a 0.8mA reference.

• Required current for CD stage is 0.2 mA, hence mirror equation gives:

$\frac{I_{DMI1}}{I_{REF}} = \frac{\left(W/L\right)_{MI1}}{\left(W/L\right)_{REF}} \implies \frac{0.2}{0.8} = \frac{\left(W/L\right)_{MI1}}{\left(W/L\right)_{REF}} \implies \frac{1}{2 \text{ to } 8}$

• Similarly, for CS stage the ratio is 5 to 8

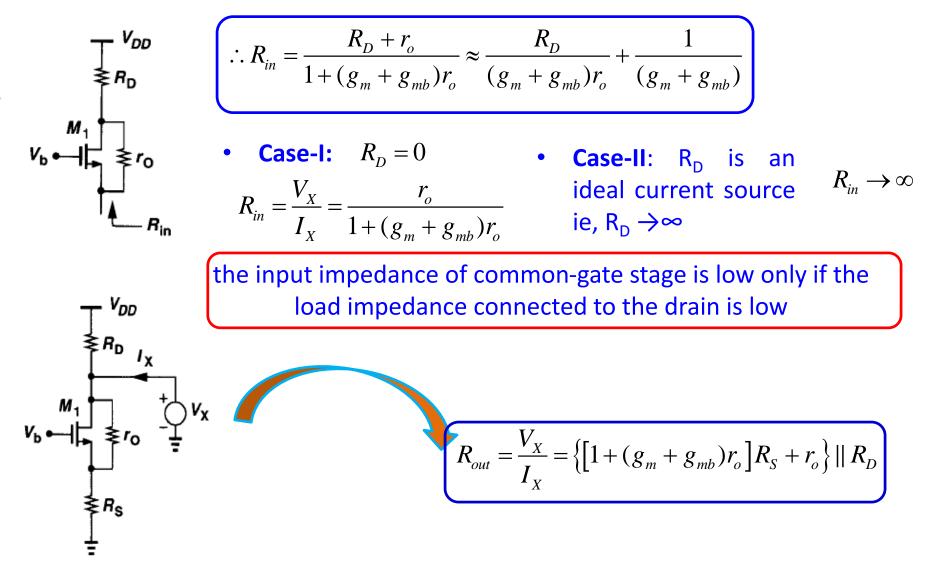

#### **Common Gate Stage**

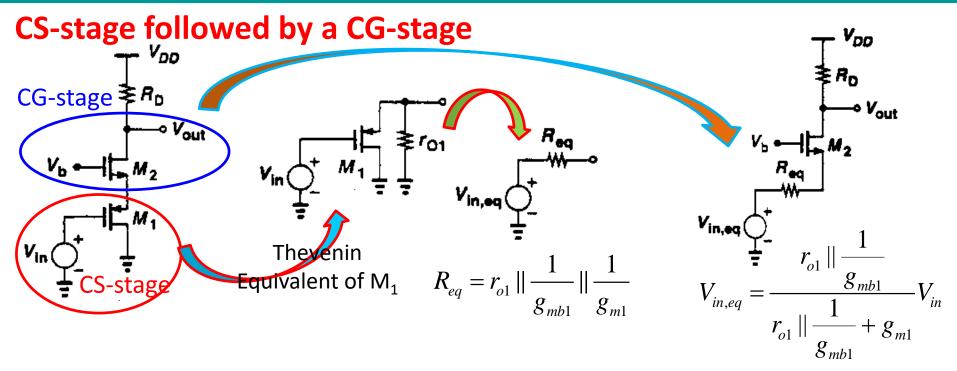

• Use the CG stage expression to obtain the small signal voltage gain as:

$$\frac{V_{out}}{V_{in}} = A_{v} = \frac{(g_{m2} + g_{mb2})r_{o2} + 1}{r_{o2} + \left[1 + (g_{m2} + g_{mb2})r_{o2}\left(r_{o1} \| \frac{1}{g_{mb1}} \| \frac{1}{g_{m1}} \right)\right] + R_{D}} R_{D} \frac{r_{o1} \| \frac{1}{g_{mb1}} \frac{1}{g_{mb1}} + \frac{1}{g_{m2}}}{r_{o1} \| \frac{1}{g_{mb1}} + \frac{1}{g_{m2}}}$$

#### significantly larger gain when compared to CS stage

### Example – 3

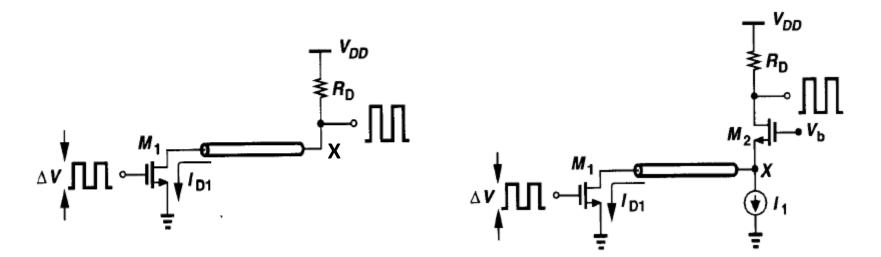

The CS-stage in both the following circuits senses  $\Delta V$  at node X and delivers a proportional current to a 50 $\Omega$  transmission line.

(a) Calculate small signal gain at low frequencies.

(b) What condition is necessary to minimize wave reflections at node X

### **Cascode Stage**

- <u>Terminology</u>: It stems from erstwhile vacuum tube in which cathodes were cascaded. In practice, the output of first tube (anode) feeds the input of second tube (cathode)

- <u>Configuration</u>: CG-stage in cascade with CS-stage

→ actually CS-stage is called the main device whereas CG is called the cascode device

- <u>Basic Idea</u>: combines high input impedance and large transconductance of CS with the current buffering property and the superior high frequency response of CG stage

- <u>Cascode Provides</u>: wider bandwidth, increased small-signal gain, high input impedance, customized output impedance

- <u>Applications:</u> Current Source, Small-Signal Amplifier

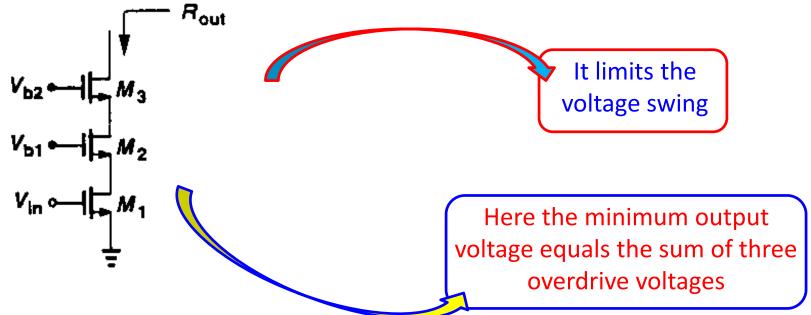

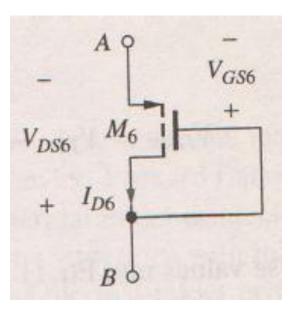

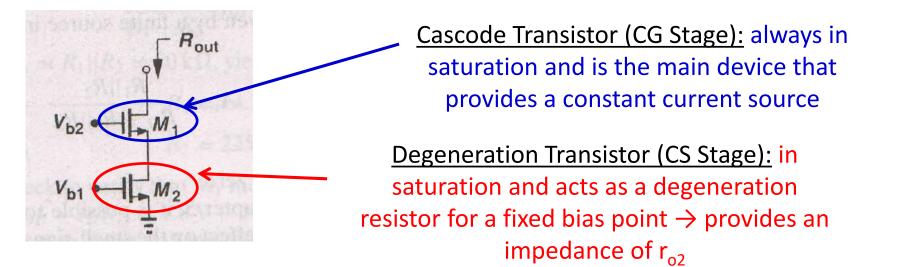

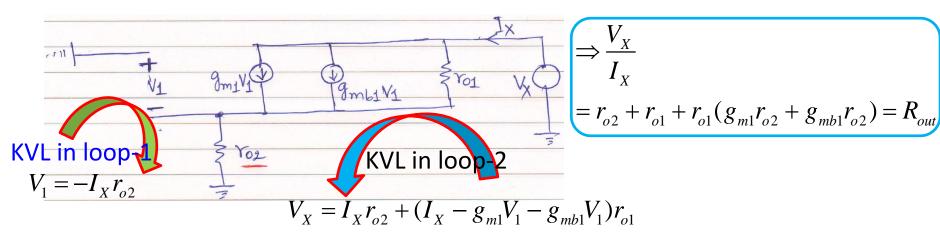

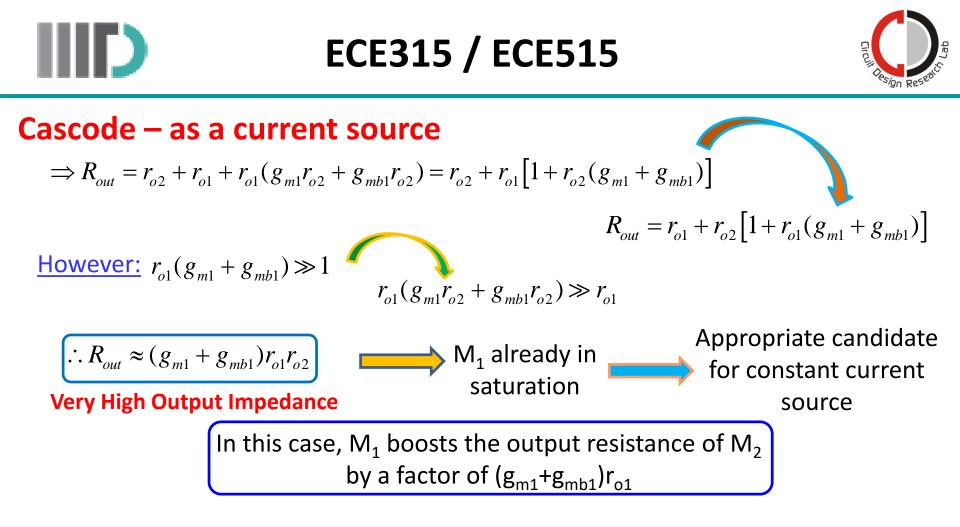

### **Cascode – as a current source**

Current Source: requires very high output impedance

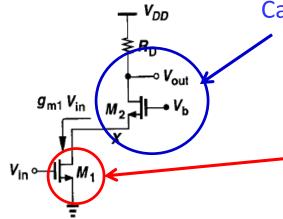

### **Cascode – Amplifier**

Cascode device (in CG)  $\rightarrow$  in saturation  $\rightarrow$  routes the current generated by main device to R<sub>D</sub>

main device (in CS)  $\rightarrow$  in saturation  $\rightarrow$  converts and amplifies an input voltage signal into output current

**Bias Conditions of Cascode:**

- For M<sub>1</sub> to be in saturation:  $V_X > V_{in} V_{T1}$  $\Rightarrow V_b - V_{GS2} > V_{in} - V_{T1} \Rightarrow V_b > V_{in} + V_{GS2} - V_{T1}$

- For M<sub>2</sub> to be in saturation:  $V_{out} V_X \ge V_{GS2} V_{T2}$

$$\Rightarrow V_{out} \geq V_{in} - V_{T1} + V_{GS2} - V_{T2}$$

$$V_{OV1} + V_{OV2}$$

Minimum output voltage equals overdrive voltage of  $M_1$  and  $M_2 \rightarrow$ addition of  $M_2$  reduces the output voltage swing by  $V_{GS2}$ - $V_{T2}$

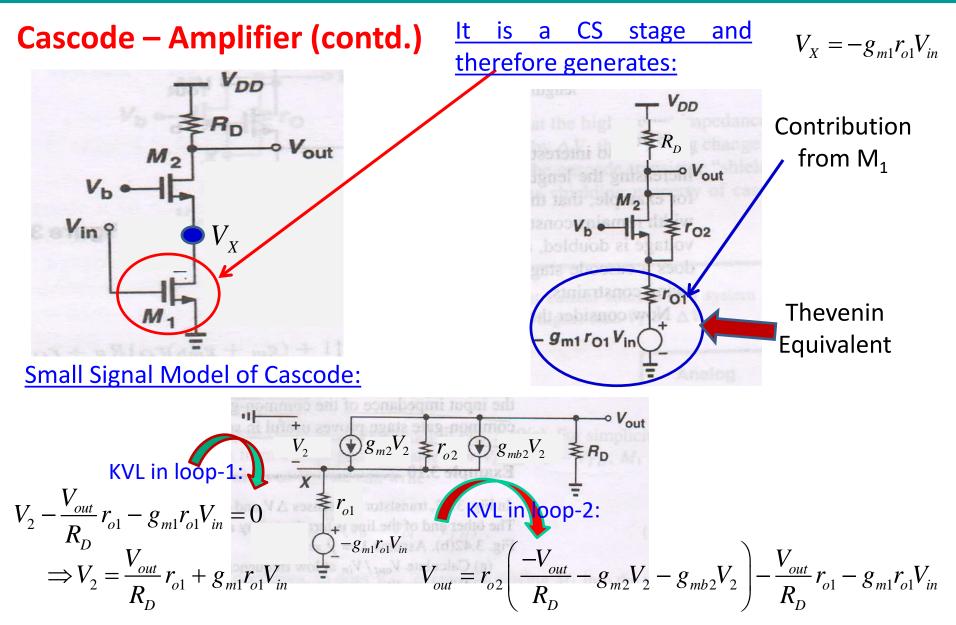

### **Cascode – Amplifier (contd.)**

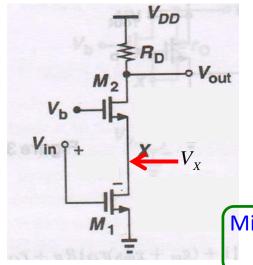

Output Impedance: ability to synthesize desired output impedance

### **Cascode – Amplifier (contd.)**

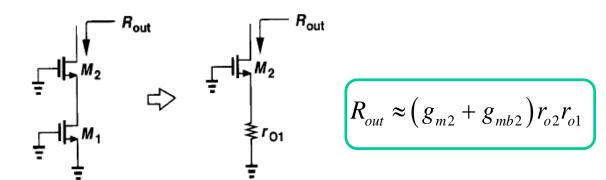

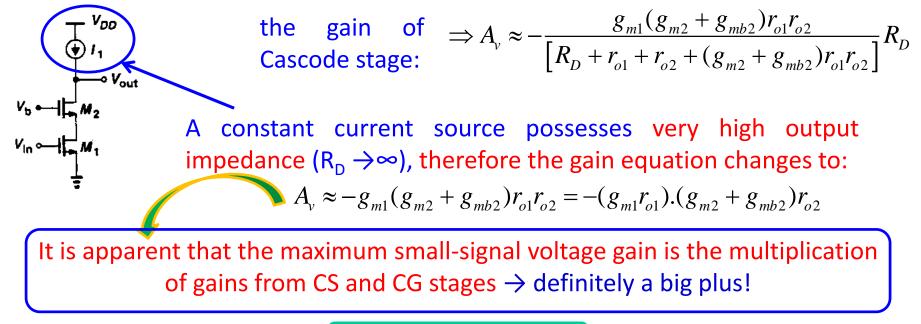

$$R_{out} \approx \left(g_{m2} + g_{mb2}\right) r_{o2} r_{o1}$$

## Cascode – Amplifier (contd.)

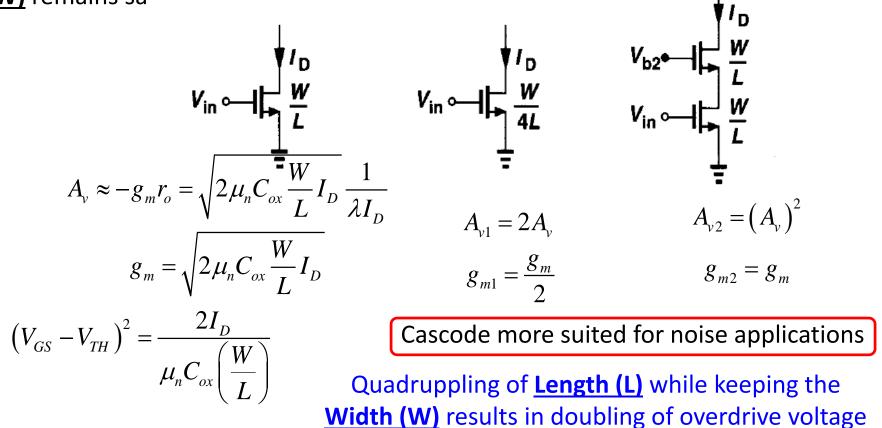

**Discussion with respect to alteration in dimension**

What happens if Length (L) of the main device is quadrupled while the Width (W) remains sa

For identical devices, cascode also exhibits doubling of overdrive voltage

## **Shielding Property of Cascode**

Cascode amplifier and Cascode current source  $\rightarrow$  could be used in applications where the output varies drastically due to any reason!  $\rightarrow$  This variation doesn't affect the subsequent sections greatly  $\rightarrow$  shielding property of Cascode

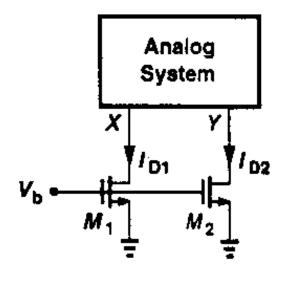

**Example:** Two identical NFETs are used to generate constant current sources. However, due to internal circuitry of the system,  $V_x$  is higher than  $V_y$  by  $\Delta V$ .

Q: determine the resulting difference between  $I_{D1}$  and  $I_{D2}$  if  $\lambda \neq 0$

$$I_{D1} = \frac{1}{2} \mu_n C_{ox} (V_b - V_T)^2 (1 + \lambda V_X)$$

$$V_{DS2}$$

$$I_{D2} = \frac{1}{2} \mu_n C_{ox} (V_b - V_T)^2 (1 + \lambda V_Y)$$

$$I_{D1} - I_{D2} = \frac{1}{2} \mu_n C_{ox} (V_b - V_T)^2 (\lambda \Delta V)$$

## **Shielding Property of Cascode (contd.)**

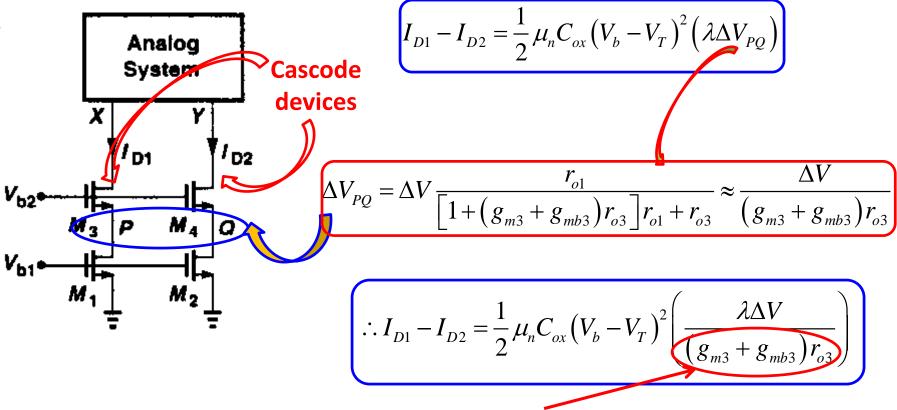

Q: Add Cascode devices to M1 and M2 and then check the difference between  $I_{D1}$  and  $I_{D2}$  if  $\lambda \neq 0$

This is a large value and thus the Cascode structure gives smaller variation → perfect example of Shielding property!!!

## **Triple Cascode**

Cascoding can be extended to three or more devices to achieve higher output impedance