# <u>Lecture – 11</u>

# Date: 15.09.2016

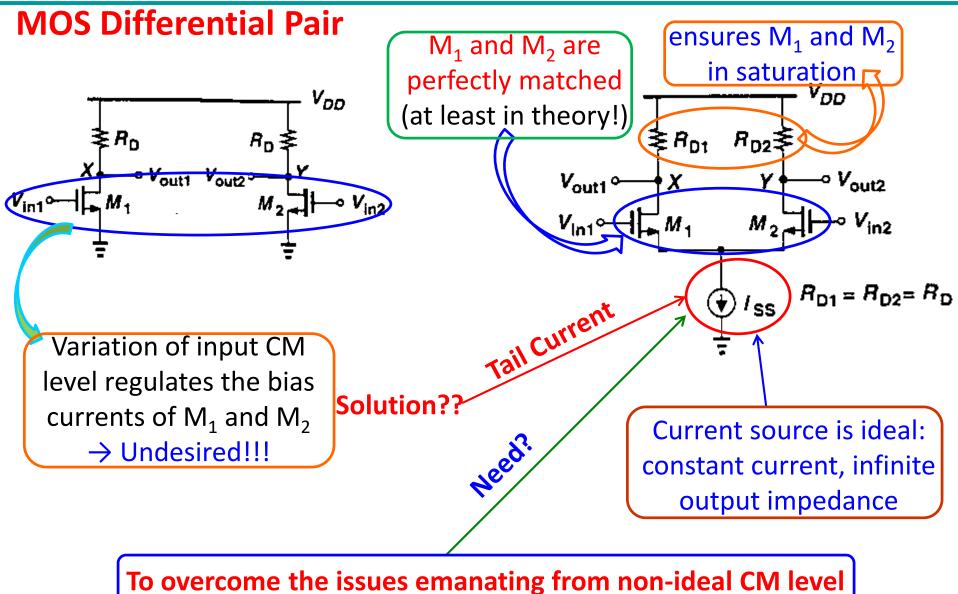

- MOS Differential Pair

- Quantitative Analysis differential input

- Small Signal Analysis

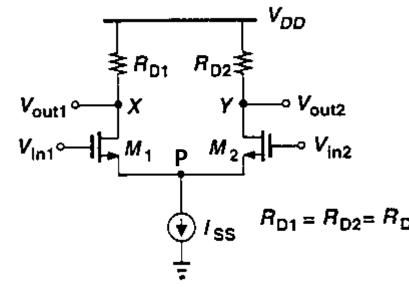

#### **Qualitative Analysis – differential input**

• Let us check the effect of  $V_{in1} - V_{in2}$  variation from  $-\infty$  to  $\infty$

- V<sub>in1</sub> is much more –ve than V<sub>in2</sub> then:

- M<sub>1</sub> if OFF and M<sub>2</sub> is ON

- $I_{D2} = I_{SS}$

- $V_{out1} = V_{DD}$  and  $V_{out2} = V_{DD} I_{SS}R_D$

- V<sub>in1</sub> is brought closer to V<sub>in2</sub> then:

- M<sub>1</sub> gradually turns ON and M<sub>2</sub> is ON

- Draws a fraction of I<sub>SS</sub> and lowers V<sub>out1</sub>

- I<sub>D2</sub> decreases and V<sub>out2</sub> rises

$$V_{in1} = V_{in2}$$

•  $V_{out1} = V_{out2} = V_{DD} - I_{SS}R_D/2$

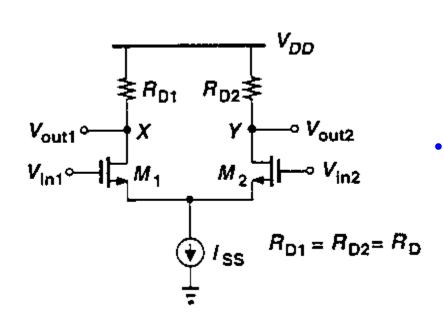

# **MOS Differential Pair**

### **Qualitative Analysis – differential input**

• Let us check the effect of  $V_{in1} - V_{in2}$  variation from  $-\infty$  to  $\infty$

- V<sub>in1</sub> becomes more +ve than V<sub>in2</sub> then:

- M<sub>1</sub> if ON and M<sub>2</sub> is ON

- M<sub>1</sub> carries greater I<sub>ss</sub> than M<sub>2</sub>

- For sufficiently large  $V_{in1} V_{in2}$ :

- All of the  $I_{ss}$  goes through  $M_1 \rightarrow M_2$  is OFF

- $V_{out1} = V_{DD} I_{SS}R_{D}$  and  $V_{out2} = V_{DD}$

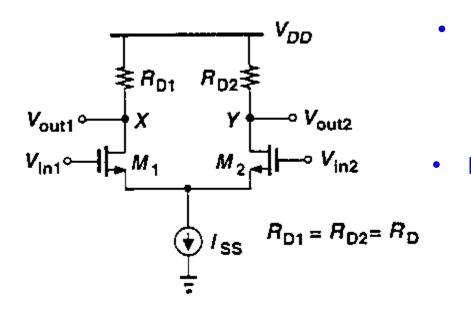

## **MOS Differential Pair**

<u>Qualitative Analysis – differential input</u>

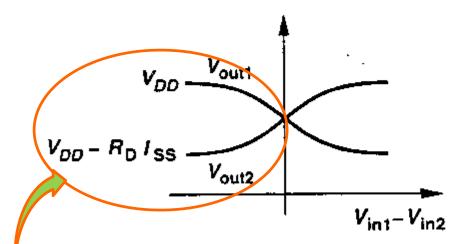

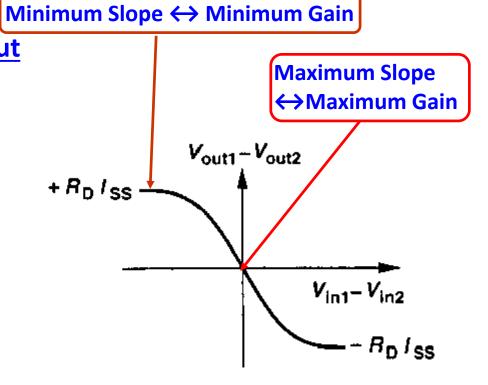

Plotting V<sub>out1</sub> – V<sub>out2</sub> versus V<sub>in1</sub> – V<sub>in2</sub>

The maximum and minimum levels at the output are well defined and is independent of input CM level (V<sub>in,cm</sub>)

The circuit becomes more nonlinear as the input voltage swing increases (i.e.,  $V_{in1} - V_{in2}$ increases)  $\leftrightarrow$  at  $V_{in1} = V_{in2}$ , the circuit is said to be in equilibrium

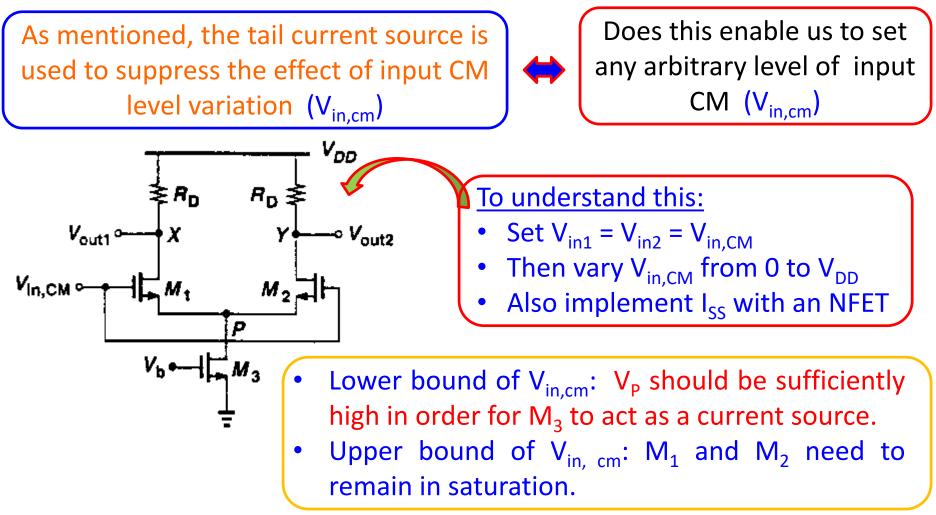

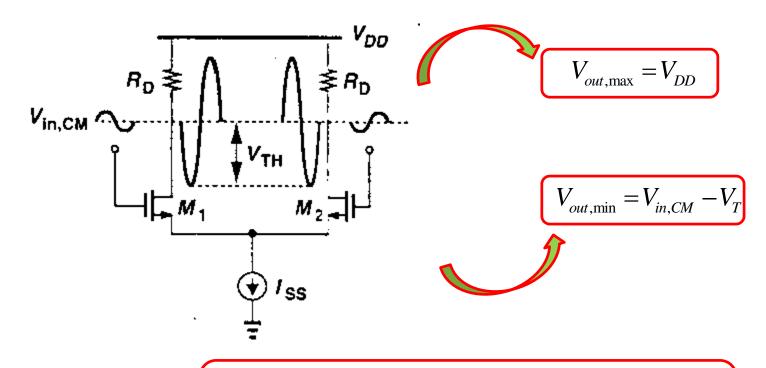

#### <u>Qualitative Analysis – common mode input</u>

• Now let us consider the common mode behavior of the circuit

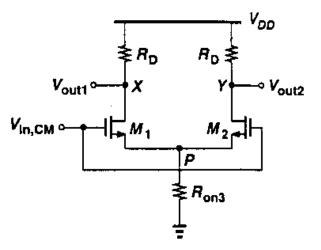

#### <u>Qualitative Analysis – common mode input</u>

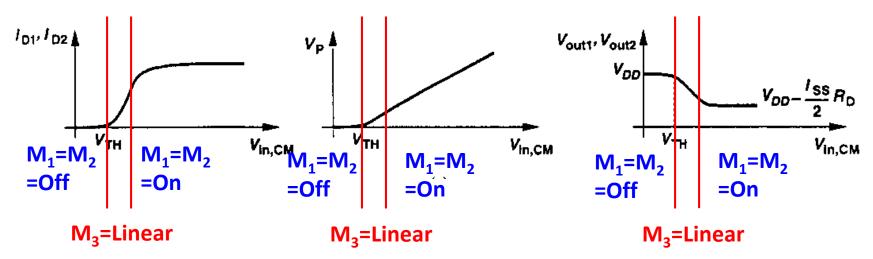

- What happens when V<sub>in,CM</sub> = 0?

- M<sub>1</sub> and M<sub>2</sub> will be OFF and M<sub>3</sub> can be in <u>triode</u> for high enough V<sub>b</sub>

- I<sub>D1</sub> = I<sub>D2</sub> = 0 ← circuit is incapable of amplification

- Now suppose V<sub>in,CM</sub> becomes more +ve

- $M_1$  and  $M_2$  will turn ON if  $V_{in,CM}$  exceeds  $V_T$

- $I_{D1}$  and  $I_{D2}$  will continue to rise with the increase in  $V_{in,CM}$

- $V_P$  will track  $V_{in,CM}$  as  $M_1$  and  $M_2$  work like a source follower

- For high enough  $V_{in,CM}$ ,  $M_3$  will be in saturation as well

- If V<sub>in,CM</sub> rises further

- $M_1$  and  $M_2$  will remain in saturation if:

#### **Qualitative Analysis – common mode input**

• For M<sub>1</sub> and M<sub>2</sub> to remain in saturation:

$$V_{GS1,2} - V_T \le V_{DS1,2} \qquad \Rightarrow V_{in,CM} - V_T \le V_{DD} - \frac{I_{SS}}{2}R_D \qquad \Rightarrow V_{in,CM} \le V_T + V_{DD} - \frac{I_{SS}}{2}R_D$$

$$\therefore (V_{in,CM})_{\max} = V_T + V_{DD} - \frac{I_{SS}}{2}R_D$$

The lowest value of V<sub>in,CM</sub> is determined by the need to keep the constant current source operational:

$$V_{in,CM} - V_{GS1,2} \ge V_{GS3} - V_T$$

$$\Rightarrow V_{in,CM} \ge V_{GS1,2} + (V_{GS3} - V_{T3})$$

$$V_{GS1,2} + (V_{GS3} - V_T) \le V_{in,CM} \le \min\left[V_{DD} - \frac{I_{SS}}{2}R_D + V_T, V_{DD}\right]$$

### **MOS Differential Pair**

<u>Qualitative Analysis – common mode input</u>

• Thus, V<sub>in,CM</sub> is bounded as:

$$V_{GS1,2} + (V_{GS3} - V_T) \le V_{in,CM} \le \min\left[V_{DD} - \frac{I_{SS}}{2}R_D + V_T, V_{DD}\right]$$

• Summary:

**Qualitative Analysis – common mode input**

• How large can the output voltage swings of a differential pair be?

The higher the input CM level, the smaller the allowable output swings.

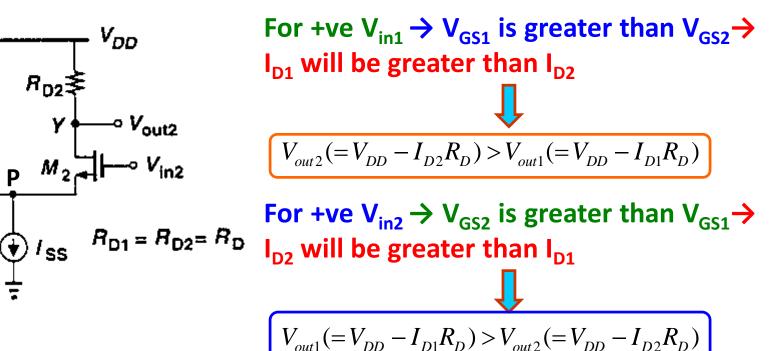

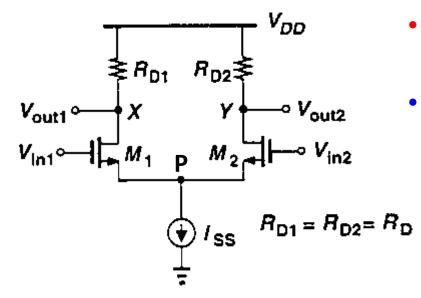

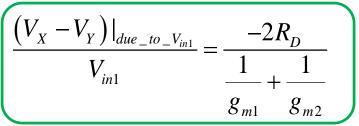

**Quantitative Analysis – differential input**

It is thus apparent that the differential pair respond to differentialmode signals  $\rightarrow$  by providing differential output signal between the two drains

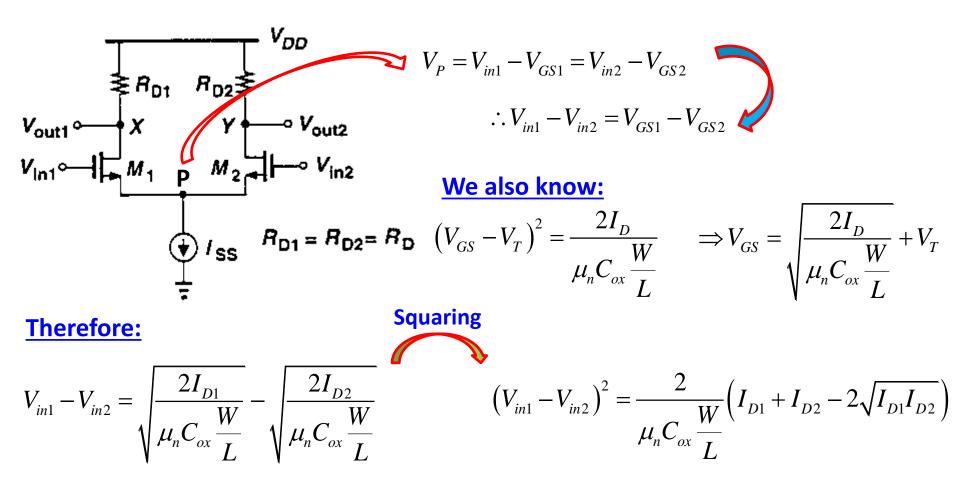

# **Differential Pair – Large Signal Analysis**

<u>Quantitative Analysis – differential input</u>

- The idea is to define  $I_{D1}$  and  $I_{D2}$  in terms of input differential signal  $V_{in1} V_{in2}$

- The circuit doesn't include connection details considering that these drain current equations do not depend on the external circuitries

• Assumptions: M<sub>1</sub> and M<sub>2</sub> are always in saturation; differential pair is perfectly matched; channel length modulation is not present

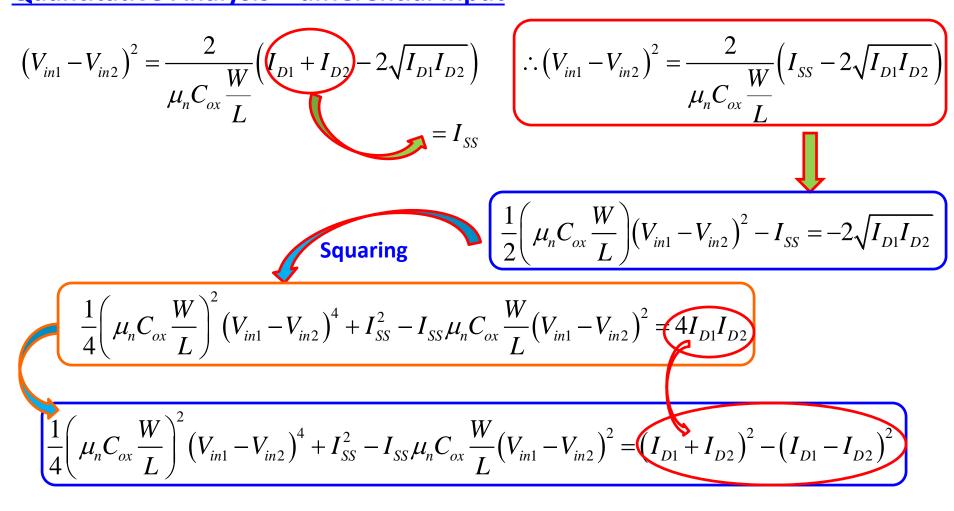

$$(I_{D1} - I_{D2})^{2} = -\frac{1}{4} \left( \mu_{n} C_{ox} \frac{W}{L} \right)^{2} \left( V_{in1} - V_{in2} \right)^{4} + I_{SS} \mu_{n} C_{ox} \frac{W}{L} \left( V_{in1} - V_{in2} \right)^{2}$$

$$I_{D1} - I_{D2} = \frac{1}{2} \left( \mu_{n} C_{ox} \frac{W}{L} \right) \left( V_{in1} - V_{in2} \right) \sqrt{\frac{4I_{SS}}{\mu_{n} C_{ox} \frac{W}{L}} - \left( V_{in1} - V_{in2} \right)^{2}}$$

#### **Observations**

- $I_{D1} I_{D2}$  falls to zero for  $V_{in1} = V_{in2}$  and  $|I_{D1} I_{D2}|$  increases with increase in  $|V_{in1} V_{in2}|$

- Therefore,  $I_{D1} I_{D2}$  is an odd function of  $V_{in1} V_{in2}$

- Its important to notice that I<sub>D1</sub> and I<sub>D2</sub> are even functions of their respective gate-source voltage

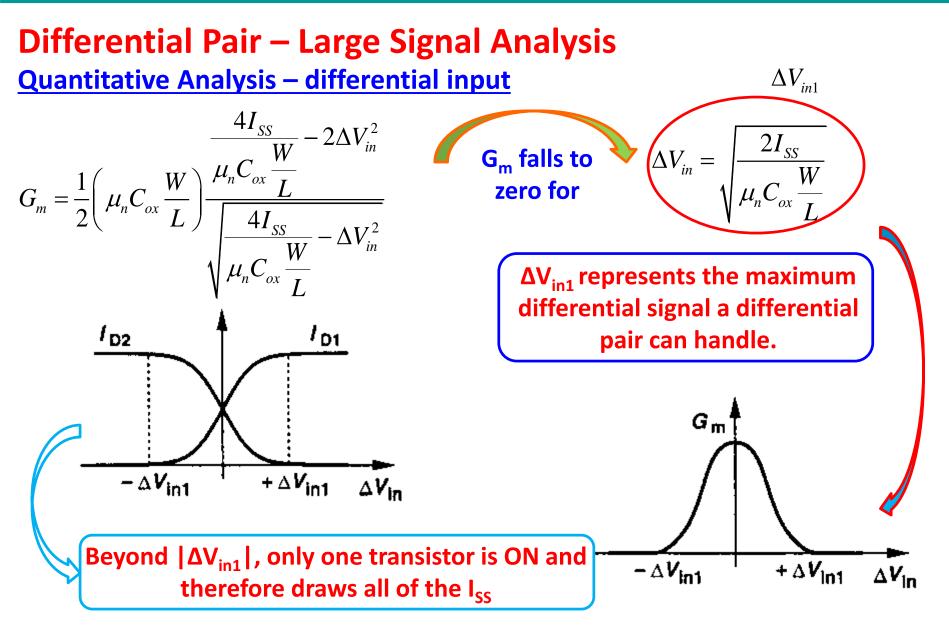

• Equivalent  $G_m$  of  $M_1$  and  $M_2 \rightarrow$  its effectively the slope of the characteristics

Lets denote:

$$I_{D1} - I_{D2} = \Delta I_D$$

$V_{in1} - V_{in2} = \Delta V_{in}$

$\Delta I_D = \frac{1}{2} \left( \mu_n C_{ox} \frac{W}{L} \right) \Delta V_{in} \sqrt{\frac{4I_{SS}}{\mu_n C_{ox} \frac{W}{L}} - \Delta V_{in}^2}$

For  $\Delta V_{in} = 0$ :  $G_m = \frac{\partial \Delta I_D}{\partial \Delta V_{in}} = \sqrt{\mu_n C_{ox} \frac{W}{L}} I_{SS}$

Furthermore:  $V_{out1} - V_{out2} = R_D \Delta I = R_D G_m \Delta V_{in}$

$\frac{\partial \Delta I_D}{\partial \Delta V_{in}} = \frac{1}{2} \left( \mu_n C_{ox} \frac{W}{L} \right) \frac{\frac{4I_{SS}}{\mu_n C_{ox} \frac{W}{L}} - 2\Delta V_{in}^2}{\sqrt{\frac{4I_{SS}}{\mu_n C_{ox} \frac{W}{L}} - \Delta V_{in}^2}}$

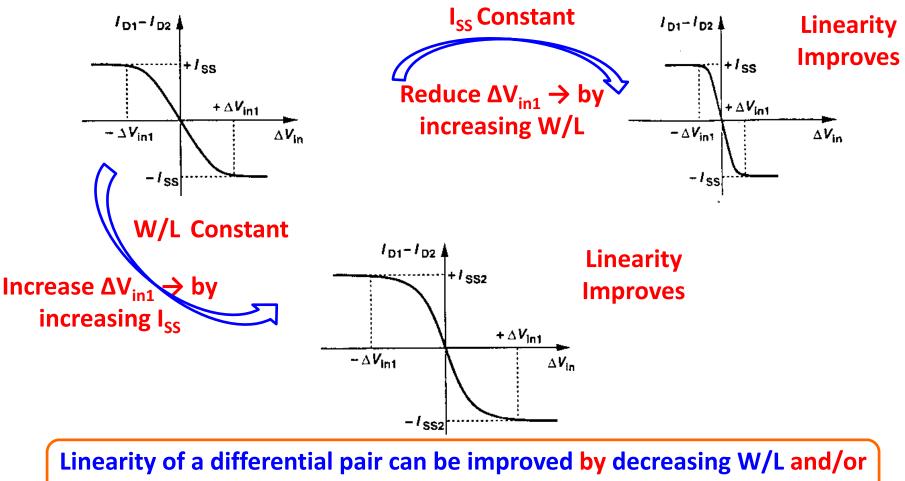

increasing I<sub>ss</sub>

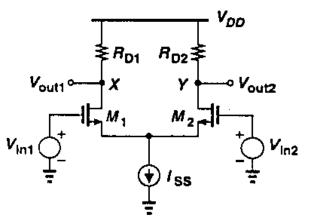

# **MOS Differential Pair – small signal analysis**

**Quantitative Analysis – differential input**

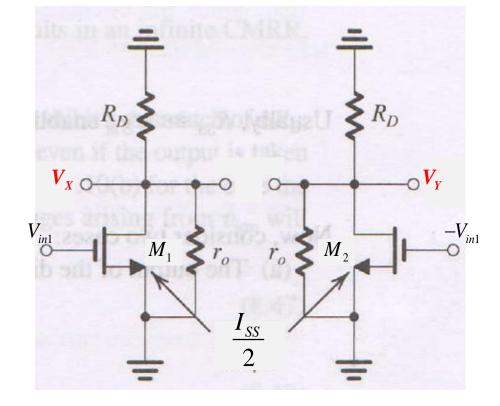

• From large signal analysis we achieved:

$$\therefore |A_{v}| = \frac{V_{out1} - V_{out2}}{\Delta V_{in}} = g_{m}R_{D}$$

$$\therefore |A_{v}| = \frac{V_{out1} - V_{out2}}{\Delta V_{in}} = \left( \mu_{n} C_{ox} \frac{W}{L} I_{SS} R_{D} \right)$$

At equilibrium, this is g<sub>m</sub>

We apply small signals to V<sub>in1</sub> and V<sub>in2</sub> and assume M<sub>1</sub> and M<sub>2</sub> are already operating in saturation.

- How to arrive at this result using small signal analysis?

- Two techniques

- Superposition method

- Half-circuit concept

# **MOS Differential Pair – small signal analysis**

- <u>Method-I</u>: Superposition technique the idea is to see the effect of V<sub>in1</sub> and V<sub>in2</sub> on the output and then combine to get the differential small signal voltage gain

- First set, V<sub>in2</sub> = 0

V<sub>DD</sub>

⊸ V<sub>out2</sub>

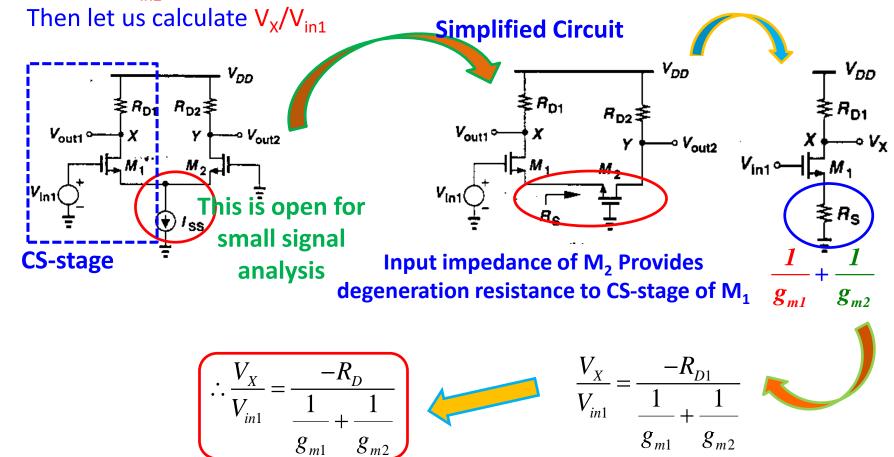

## **MOS Differential Pair – small signal analysis**

combine the expressions to calculate  $\left( \frac{(V_X - V_Y)}{|_{due\_to\_V_{in1}}} \right)$ small signal voltage only due to V<sub>in1</sub>

## **MOS Differential Pair – small signal analysis**

For matched transistors:  $(V_X - V_Y)|_{due_to_V_{in1}} = -g_m R_D V_{in1}$

• Similarly:

$$(V_X - V_Y)|_{due_to_V_{in2}} = g_m R_D V_{in2}$$

• Superposition gives

$$A_v = \frac{(V_X - V_Y)_{total}}{V_{in2} - V_{in1}} = -g_m R_D$$

- The magnitude of differential gain is g<sub>m</sub>R<sub>D</sub> regardless of how the inputs are applied

- The gain will be halved if single ended output is considered

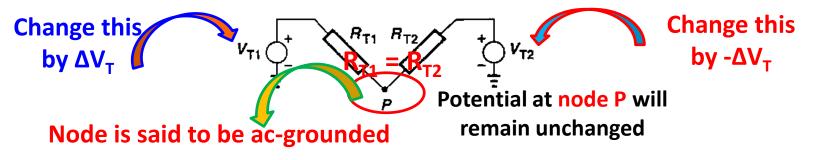

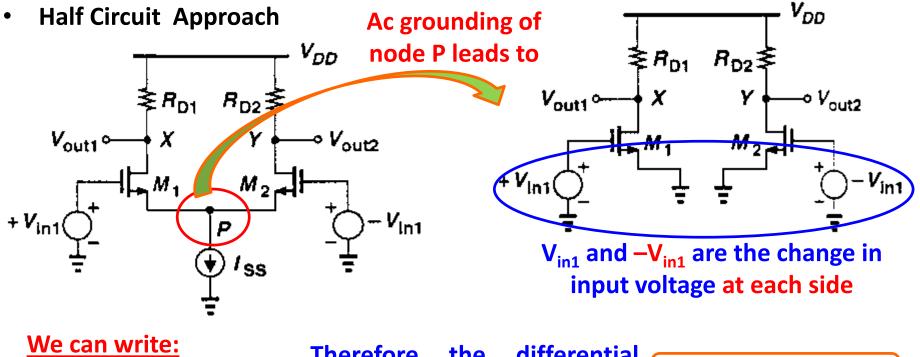

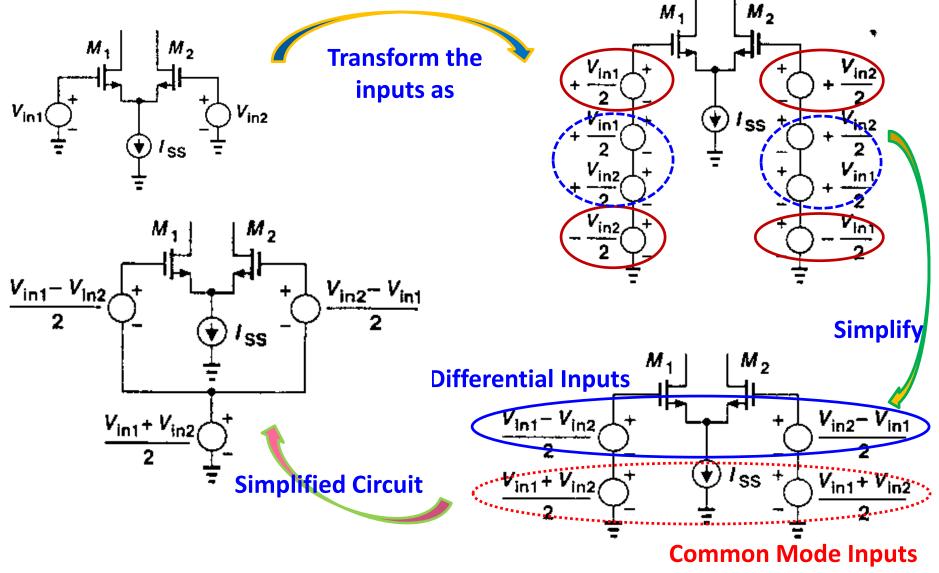

- Half Circuit Approach

- If a fully symmetric differential pair senses differential inputs (i.e, the two inputs change by equal and opposite amounts from the equilibrium condition), then the concept of half circuit can be applied.

## **MOS Differential Pair – small signal analysis**

$\frac{V_X}{V_{in1}} = -g_m R_D$

Therefore the differential output can be expressed as:

$V_X - V_Y = 2V_{in1} \left(-g_m R_D\right)$

Thus the small signal voltage given is:

$$A_{v} = \frac{V_{X} - V_{Y}}{2V_{in1}} = -g_{m}R_{D}$$

## **MOS Differential Pair – small signal analysis**

- How does the gain of a differential amplifier compare with a CS stage?

- For a given total bias current  $I_{SS}$ , the value of equivalent  $g_m$  of a differential pair is  $1/\sqrt{2}$  times that of  $g_m$  of a single transistor biased at the  $I_{SS}$  with the same dimensions. Thus the total gain is proportionally less.

- Equivalently, for given device dimensions and load impedance, a differential pair achieves the same gain as a CS stage at the cost of twice the bias current.

- What is the advantage of differential stage then?

- Definitely the noise suppression capability. Right?

## **MOS Differential Pair – small signal analysis**

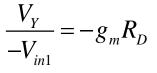

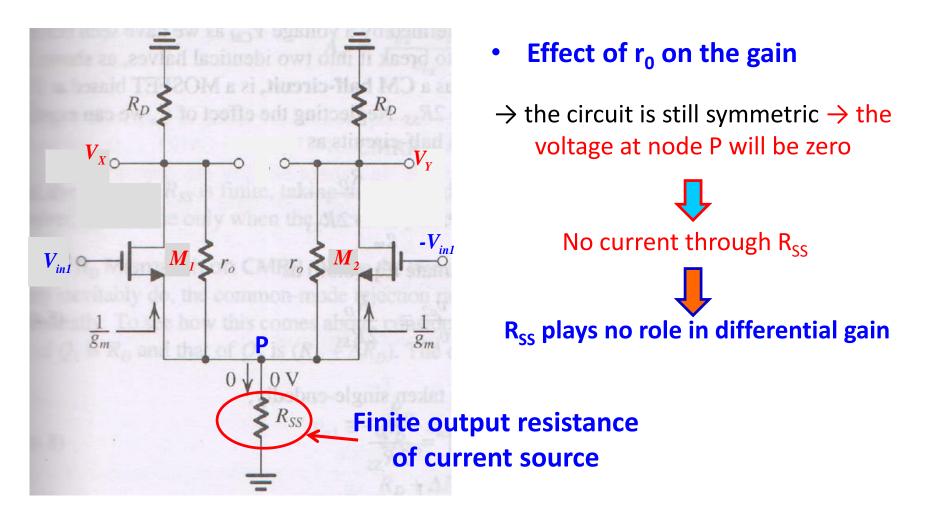

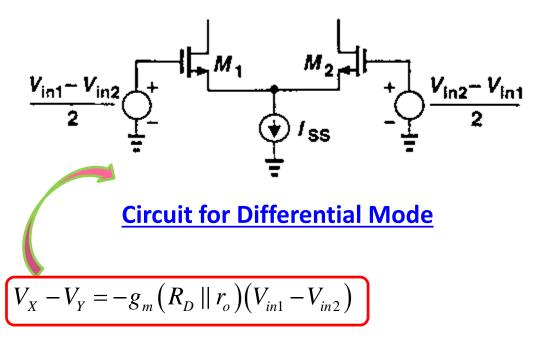

• How is gain affected if channel length modulation is considered?

## **MOS Differential Pair – small signal analysis**

The virtual ground on the source allows division of two identical CS amplifiers: → differential half circuits

$$V_X = -g_m V_{in1} (R_D \parallel r_o)$$

$$V_Y = g_m V_{in1} \left( R_D \parallel r_o \right)$$

$$\Rightarrow V_X - V_Y = -g_m (2V_{in1}) (R_D \parallel r_o)$$

$$\therefore A_{v} = \frac{V_{X} - V_{Y}}{2V_{in1}} = -g_{m} \left( R_{D} \parallel r_{o} \right)$$

## Small signal analysis – asymmetric inputs

## Small signal analysis – asymmetric inputs

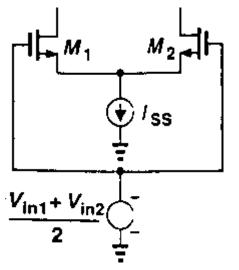

**Circuit for Common Mode**

If the circuit is fully symmetric and I<sub>SS</sub> is ideal current source, then M<sub>1</sub> and M<sub>2</sub> draws half of I<sub>SS</sub> and is independent of V<sub>in,CM</sub>. The V<sub>x</sub> and V<sub>y</sub> experience no change as V<sub>in,CM</sub> varies. In essence, the circuit simply amplifies the difference between V<sub>in1</sub> and V<sub>in2</sub> while eliminating the effect of V<sub>in,CM</sub>.