Date: 03.09.2015

### **Lecture – 9**

Biasing in MOS Amplifier Circuits

### **Biasing using Single Power Supply**

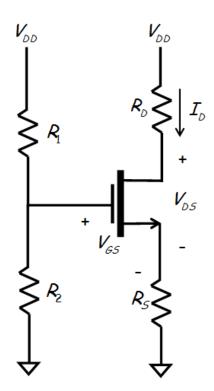

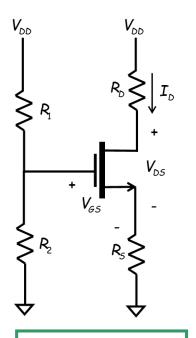

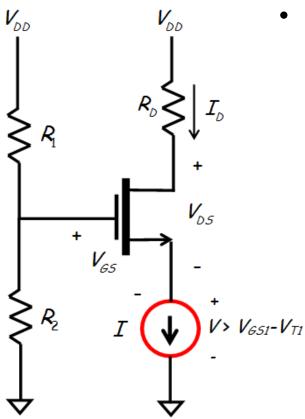

The general form of a single-supply MOSFET amplifier biasing circuit is:

We typically attempt to satisfy three main bias design goals:

#### 1) Maximize Gain

Typically, the small-signal **voltage gain** of a MOSFET amplifier will be proportional to transconductance  $g_m$ .

$$A_{\rm m} \propto g_{\rm m}$$

Thus, to maximize the amplifier voltage gain, we must **maximize** the MOSFET transconductance.

### Biasing using Single Power Supply (contd.)

Q: What does this have to do with **D.C. biasing?**

A: Recall that the transconductance depends on the **DC excess gate voltage**:

$$g_{\mathsf{m}} = 2 K \left( V_{\mathsf{GS}} - V_{\mathsf{T}} \right)$$

- Another way to consider transconductance is to express it in terms of DC drain current  $I_D$ .

- Recall this DC current is related to the DC excess gate voltage (in saturation!) as:

$$I_D = K (V_{GS} - V_T)^2$$

$\Rightarrow$   $(V_{GS} - V_T) = \sqrt{\frac{I_D}{K}}$

And so transconductance can be alternatively expressed as:

$$g_{m} = 2K(V_{GS} - V_{T}) = 2K\sqrt{\frac{I_{D}}{K}} = 2\sqrt{KI_{D}}$$

### Biasing using Single Power Supply (contd.)

• Therefore, the amplifier voltage gain is typically **proportional** to the square-root of the DC drain current:

$$A \propto \sqrt{I_D}$$

To maximize  $A_{v}$ , maximize  $I_{D}$

#### 2) Maximize Voltage Swing

Recall that if the DC drain voltage  $V_D$  is biased too close to  $V_{DD}$ , then even a small **small-signal** drain voltage  $v_d(t)$  can result in a **total** drain voltage that is too **large**, i.e.:

$$V_D(t) = V_D + V_d(t) \geq V_{DD}$$

In other words, the MOSFET enters **cutoff**, and the result is a **distorted** signal!

### **Biasing using Single Power Supply (contd.)**

- To avoid this (to allow  $v_d(t)$  to be as large as possible without MOSFET entering cutoff), we need to bias our MOSFET such that the DC drain voltage  $V_D$  is as **small** as possible.

- Note that the drain voltage is:  $V_D = V_{DD} R_D I_D$

- Therefore  $V_D$  is minimized by designing the bias circuit such that the DC drain current  $I_D$  is as **large** as possible.

- However, we must **also** consider the signal distortion that occurs when the MOSFET enters **triode**. This of course is avoided if the total drain-to-source voltage remains greater than the excess gate voltage, i.e.:

$$V_{DS}(t) = V_{DS} + V_{ds}(t) > (V_{GS} - V_{T})$$

Thus, to avoid the MOSFET triode mode—and the resulting signal distortion—we need to bias our MOSFET such that the DC voltage is as large as possible.

To minimize signal distortion, maximize  $V_{DS}$

### Biasing using Single Power Supply (contd.)

- 3) Minimize Sensitivity to changes in  $K, V_T$

- We find that MOSFETs are **sensitive** to temperature—specifically, the value of K is a function of temperature.

- Likewise, the values of K and  $V_T$  are not particularly constant with regard to the manufacturing process.

- Both of these facts lead to the requirement that our bias design be **insensitive** to the values of K and  $V_T$ . Specifically, we want to design the bias network such that the DC bias current does **not** change values when K and/or  $V_T$  does.

- Mathematically, we can express this requirement as minimizing the value:  $\frac{d I_D}{dK}$  and  $\frac{d I_D}{dV_T}$

- These derivatives can be minimized by maximizing the value of **source** resistor  $R_S$ .

### Biasing using Single Power Supply (contd.)

- So, let's recap what we have learned about designing our bias network:

- **1.** Make  $I_D$  as large as possible.

- **2.** Make  $V_{DS}$  as large as possible.

- **3.** Make  $R_S$  as large as possible.

Actually these three goals are conflicting, as they are constrained by the KVL equation of the bias circuit.

### **Biasing using Single Power Supply (contd.)**

Maximize  $A_v$  by maximizing this term.

Minimize distortion by **maximizing** this term.

<u>or</u>

$$I_D R_D + V_{DS} + I_D R_S = V_{DD}$$

But the **total** of the three terms must equal this!

Minimize sensitivity by **maximizing** this term.

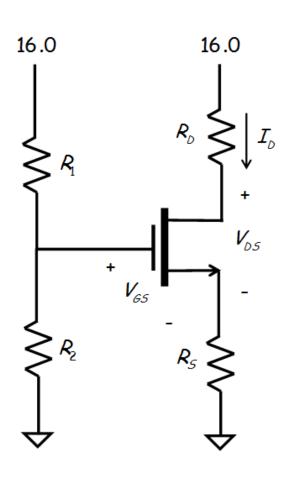

### Example - 1

• If the MOSFET has device values  $K=1.0\ ^{mA}/_{V^2}$  and  $V_T=1.0V$ , determine the resistor values to bias this MOSFET with a DC drain current of  $I_D=4.0mA$ .

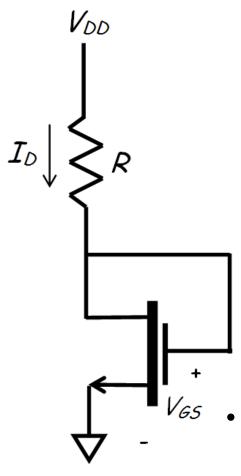

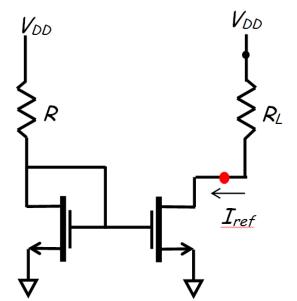

#### The MOSFET Current Mirror

Consider the following MOSFET circuit:

- Note  $V_D = V_G$ , therefore:  $V_{DS} = V_{GS}$

- and thus:  $V_{DS} = V_{GS}$

- The MOSFET is in saturation if  $V_G > V_T$ .

- We know that for a MOSFET in saturation, the drain current is:

$$I_{D} = K (V_{GS} - V_{T})^{2}$$

Say we want this current  $I_D$  to be a **specific** value—call it  $I_{ref}$ .

Since  $V_S = 0$ , we find that from the above equation, the  $V_D = \sqrt{\frac{I_{ref}}{K}} + V_T$  drain voltage must be:

### The MOSFET Current Mirror (contd.)

Likewise, from KVL we find that:

$$I_{ref} = \frac{V_{DD} - V_{D}}{R}$$

And thus the resistor value to achieve the desired drain current

$$I_{ref}$$

is:  $oldsymbol{R} = rac{oldsymbol{V_{DD}} - oldsymbol{V_{D}}}{oldsymbol{I_{ref}}}$

where:

$$V_D = \sqrt{\frac{I_{ref}}{K}} + V_T$$

Q: Why are we doing this?

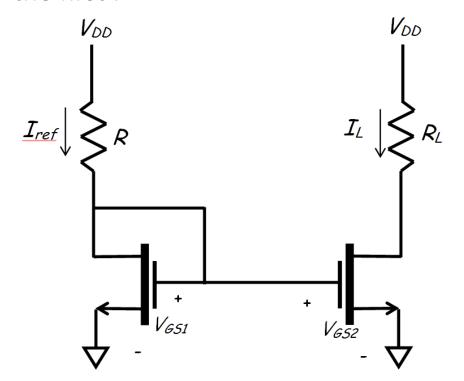

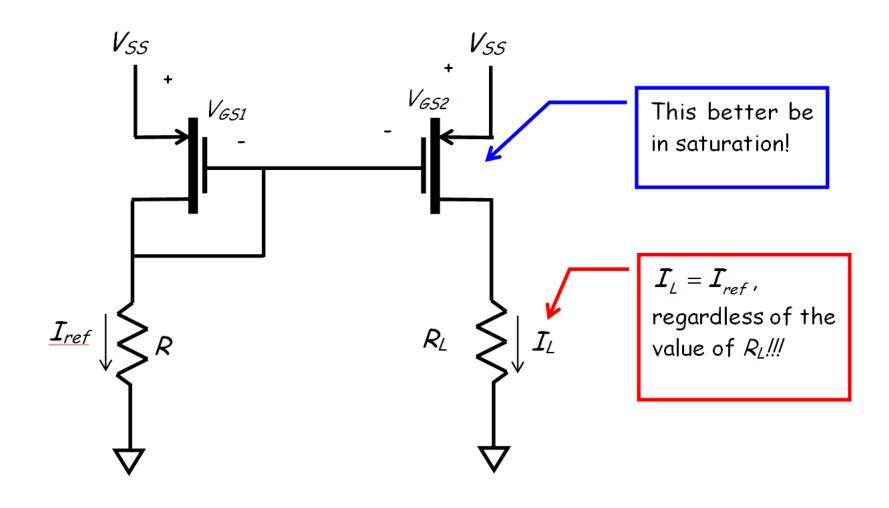

A: Say we now add another component to the circuit, with a second MOSFET that is **identical** to the first:

### The MOSFET Current Mirror (contd.)

Q: So what is current  $I_L$ ?

A: Note that the gate voltage of each MOSFET is the **same** (i.e.,  $V_{GS1} = V_{GS2}$ ), and if the MOSFETS are the **same** (i.e.,  $K_1 = K_2$ ,  $V_{T1} = V_{T2}$ ), and if the second MOSFET is likewise in **saturation**.

• The drain current  $I_L$  is:

$$I_{L} = K_{2} \left( V_{GS2} - V_{T2} \right)^{2}$$

$$= K_{1} \left( V_{GS1} - V_{T1} \right)^{2} = I_{ref}$$

Therefore, the drain current of the **second** MOSFET is **equal** to the current of the **first**!

$$I_{ref} = I_{l}$$

Q: Wait a minute! You mean to say that the current through the resistor  $R_L$  is **independent** of the value of resistor  $R_I$ ?

A: Absolutely! As long as the second MOSFET is in **saturation**, the current through  $R_L$  is equal to  $I_{ref}$ —**period**.

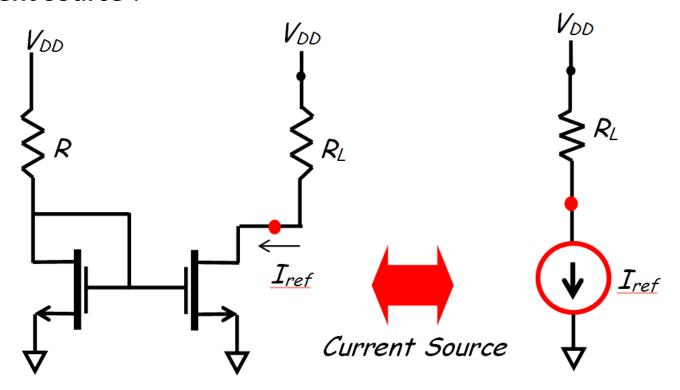

### The MOSFET Current Mirror (contd.)

• The current through  $R_L$  is independent of the value of  $R_L$  (provided that the MOSFET remains in saturation). Think about what this means—this device is a **current source**!

### The MOSFET Current Mirror (contd.)

• Remember, the second MOSFET **must** be in saturation for the current through  $R_L$  to be a constant value  $I_{ref}$ . As a result, we find that:

$$V_{DS2} > V_{GS2} - V_{T2}$$

For this example:  $V_{D2} > V_{G2} - V_{T2}$

- Since  $V_{D2}=V_{DD}-R_LI_{ref}$ , we find that  $V_{DD}-R_LI_{ref}>V_{G2}-V_{T2}=V_{G1}-V_{T1}$  the MOSFET will be in saturation if:

- Alternatively, we find the limitation on the load resistor  $R_i$ :

$$V_{DS2} > V_{GS2} - V_{T2}$$

#### The MOSFET Current Mirror (contd.)

$$R_L < rac{V_{DD} - V_{G1} + V_{T1}}{I_{ref}}$$

- We know that:  $V_{G1} = V_{DD} R I_{ref}$

- Thus we can alternatively write the above equation as:

$R_L < R + \frac{V_{T1}}{I_{ref}}$

- If the **load** resistor becomes **larger** than  $R + \frac{V_{T1}}{I_{ref}}$ , the voltage  $V_{DS2}$  will drop **below** the excess gate voltage  $V_{GS2} V_{T2}$ , and thus the second MOSFET will enter the **triode** region. As a result, the drain current will **not** equal  $I_{ref}$ —the current source will **stop working**!

- Although the circuit presented here is sometimes referred to as a current sink, understand that the circuit is clearly a way of designing a current source.

### The MOSFET Current Mirror (contd.)

We can also use PMOS devices to construct a current mirror!

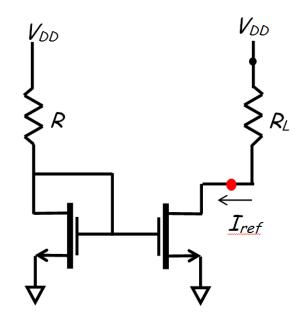

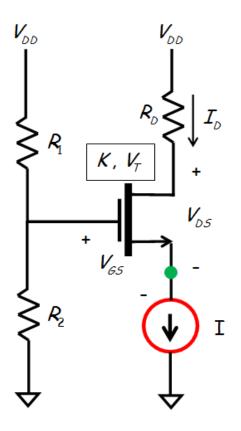

### **MOSFET Biasing using Current Mirror**

We can bias a MOSFET amplifier using a current source as:

It is evident that the DC drain current  $I_D$ , is equal to the current source I, regardless of the MOSFET values K or  $V_T$ !

Thus, this bias design maximizes drain current **stability**!

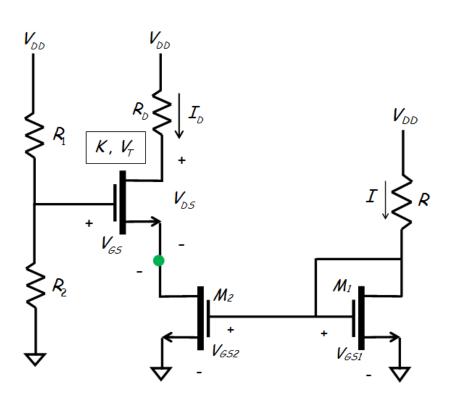

### **MOSFET Biasing using Current Mirror (contd.)**

We now know how to implement this bias design with MOSFETs—we use the current mirror to construct the current source!

• Since  $I_D = I$ , it is evident that  $V_{GS}$  must be equal to:

$$V_{GS} = \sqrt{\frac{I}{K}} + V_{T}$$

• Since the DC gate voltage is:

$$V_G = V_{DD} \left( \frac{R_2}{R_1 + R_2} \right)$$

• Therefore:

$$V_{S} = V_{G} - V_{GS}$$

$$= V_{DD} \left( \frac{R_{2}}{R_{1} + R_{2}} \right) - \left( \sqrt{\frac{I}{K}} + V_{T} \right)$$

### **MOSFET Biasing using Current Mirror (contd.)**

- Since we are biasing with a current source, we do **not** need to worry about drain current **stability**—the current source will determine the DC drain current for **all** conditions (i.e.,  $I_D = I$ ).

- We might conclude, therefore, that we should make DC source voltage  $V_S$  as **small** as possible. After all, this would allow us to **maximize** the output voltage swing (i.e., maximize  $I_DR_D$  and  $V_{DS}$ ).

- Note however, that the **source** voltage  $V_S$  of the MOSFET is numerically equal to the **drain** voltage  $V_{D2}$  (and thus  $V_{DS2}$ ) of the second MOSFET of the **current mirror**.

Q: So what?!

A: The voltage must be greater than:  $V_{GS2} - V_{T2} = V_{GS1} - V_{T1} = (V_{DD} - I_{ref}R) - V_{T1}$

in order for the **second** MOSFET to remain in **saturation**.

### **MOSFET Biasing using Current Mirror (contd.)**

There is a **minimum voltage** across the current source in order for the current source to properly operate!

• Thus, to maximize output swing, we **might** wish to set:

$$V_S = V_{GS1} - V_{T1}$$

(although to be practical, we should make  $V_S$  slightly greater than this to allow for some design margin).

Q: How do we "set" the DC source voltage  $V_S$ ?

A: By setting the DC gate voltage  $V_G!!$

### **MOSFET Biasing using Current Mirror (contd.)**

• Recall that the DC voltage  $V_{GS}$  is determined by the DC current source value **I**:

$$V_{GS} = \sqrt{\frac{I}{K}} + V_{T}$$

• and the DC gate voltage is determined by the **two** resistors  $R_1$  and  $R_2$ :

$$V_G = V_{DD} \left( \frac{R_2}{R_1 + R_2} \right)$$

• Thus, we should **select** these resistors such that:

$$V_{G} = V_{GS} + V_{S}$$

$$= \left(\sqrt{\frac{I}{K}} + V_{T}\right) + \left(V_{GS1} - V_{T1}\right)$$

$\mathbf{Q}$ : So what should the value of resistor  $\mathbf{R}_{\mathbf{D}}$  be?

A: Recall that we should set the DC drain voltage  $V_D$ :

- a) much **less** than  $V_{DD}$  to avoid **cutoff**.

- b) much greater than  $V_G V_T$  to avoid triode.

#### **MOSFET Biasing using Current Mirror (contd.)**

Thus, we compromise by setting the DC drain voltage to a point halfway

in between!

$$V_D = \frac{V_{DD} + (V_G - V_T)}{2}$$

• To achieve this, we must select the drain **resistor**  $R_D$  so that:

$$R_{D} = \frac{V_{DD} - V_{D}}{I_{D}} = \frac{V_{DD} - (V_{G} - V_{T})}{I_{D}}$$

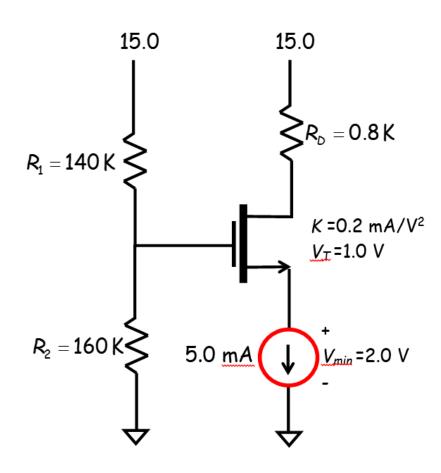

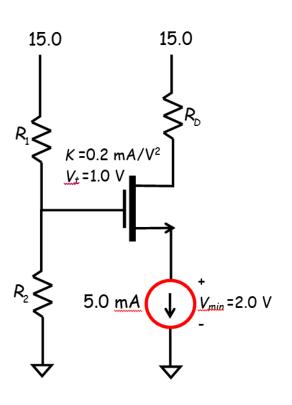

### Example – 2

Let's determine the proper resistor values to DC bias this MOSFET. The current source is 5.0 mA and has a minimum voltage of 2.0 Volts in order to operate properly

• Since  $I=I_D=5\,mA$  , we know that the value of  $V_{GS}$  should be:

$$V_{GS} = \sqrt{\frac{I}{K}} + V_{T}$$

$$= \sqrt{\frac{5.0}{0.2}} + 1.0$$

$$= 6.0 \text{ V}$$

• Assuming that we want the DC source voltage to be the minimum value of  $V_S = 2.0V$ , we need for the DC gate voltage to be:

$$V_G = V_{GS} + V_S$$

= 6.0 + 2.0

= 8.0 V

### Example – 2 (contd.)

- Thus, we need to select resistors  $R_1$  and  $R_2$  so that:  $V_G = 8.0 = V_{DD} \left( \frac{R_2}{R_1 + R_2} \right)$

- or in other words, we want:  $\left(\frac{R_2}{R_1 + R_2}\right) = \frac{8.0}{15.0}$

- Since we can make  $R_1$  and  $R_2$  large, let's assume that we want:  $R_1 + R_2 = 300 \, \text{K}$

So that

$$R_1=140~k\Omega$$

and  $R_2=160~k\Omega$  .

- Finally, we want the DC drain voltage to be:

- So that the resistor is:

$$R_{D} = \frac{V_{DD} - V_{D}}{I_{D}}$$

$$= \frac{15.0 - 11.0}{5.0}$$

$$= 0.8 \text{ K}\Omega$$

$$V_{D} = \frac{V_{DD} + (V_{G} - V_{T})}{2}$$

$$= \frac{15.0 + (8.0 - 1.0)}{2}$$

$$= 11.0 \text{ V}$$

### Example - 2 (contd.)