Date: 03.08.2015

# **Lecture-1**

- Introduction

- MOSFET

- NMOSFET Qualitative Analysis

- PMOSFET

- MOSFET Region of Operation

# **Analog CMOS Circuit Design (ECE315 / ECE515)**

**Instructor:** Dr. Mohammad S. Hashmi

TAs: Maktoomi, Dinesh, Disha

Class Timings: Monday (10:00 – 11:30) & Thursday (10:00 – 11:30)

Office Hours: Monday/Thursday (02:30 – 03:30)

**TA Hours: TBA**

**Pre-requisites:** Circuit or Network Analysis, Electronics Devices

**Course URL:**

Available at: <a href="http://www.iiitd.edu.in/~mshashmi/Teaching.html">http://www.iiitd.edu.in/~mshashmi/Teaching.html</a>

#### **Course Focus:**

MOSFET based analog circuit blocks and associated advanced circuits

#### **Course Objectives:**

On the completion of this course students should

- Have a basic knowledge of the fundamental concepts of active circuits and their analysis techniques.

- Particularly understand the theory and operation of circuit components and circuits such as Current Mirror, Linear Amplifier, Differential Amplifier, Power Amplifier etc.

- Acquire the ability to solve, analyze, design, and simulate moderately complex MOS based circuits.

#### **Lab Component:**

- Introduction to SPICE and Cadence Tools by TAs

- Advanced Topics is mostly self learning may be assisted by the TAs

#### **Evaluation:**

- Assignments 20% (6 assignments)

- Surprise Quizzes 10% (5 quizzes)

- Exams mid-sem (20%) & end-sem (20%)

- Project 30%

#### **Attendance and Classroom Behavior:**

- Attendance not mandatory

- Students will be responsible for any notes, announcements etc. made during the class

- Prompt arrival to the class is requested

- No eating, drinking, smoking allowed in the class

#### **Text Books:**

- Design of Analog CMOS Circuits by Behzad Razavi

- CMOS Analog Circuit Design by Allen & Holberg

#### **Other Recommended Books:**

- Microelectronic Circuit Design **by** Jaeger & Blalock

- Analog Integrated Circuit Design by Johns & Martin

#### **Course Website:**

http://www.iiitd.edu.in/~mshashmi/Teaching.html

Info related to ECE315 / ECE515 can be found here

## Why Analog?

- All the world is an analog stage and digital circuits play only bit parts.

Anonymous

- It's bad enough that hundreds of people are already "designing" CMOS VLSI without any significant knowledge of silicon devices and circuits and sometimes without much idea of the physics of hardware in the broader sense. As electronic systems become increasingly complex, this type of design will inevitably dominate, certainly for large-scale digital systems. But I wonder how many potentially useful ideas in the meadowlands of analog circuits will never be discovered because the world of the twenty-first century was taught that analog is dead?

#### Barrie Gilbert, "Where do little circuits come from?"

- As an old analog guru once said when comparing the analog and digital disciplines, "Any idiot can count to one, but analog design requires the engineer to make intelligent trade-offs to optimize a circuit." Analog design is not black or white as in "ones" and "zeros;" analog design is shades of gray.

- Samual Wilensky, "Reflections of a dinosaur"

## Some Thoughts!!!

Analog circuit design is like chess -just because you know how the pieces move doesn't mean you know how to play the game.

#### - Patrick M. Lahey

- Since this course deals in analog IC design, we take to heart a quote from Chris Manglesdorf (Analog Devices) at ISSCC '96, where he said that "Analog circuit designers tend to think of themselves as lone cowboys, brave pioneers, creative and independent types, in contrast to the herd animals of the digital IC world"

- Some thirty years ago, I asserted at a seminar presented at UC Berkeley that the art of analog design demanded 30% attention to the signal path and 70% to biasing. The comment was met with tolerant disbelief. However, after having taught this maxim widely and persistently during the intervening decades, I find no reason to change my mind.

-BARRIE GILBERT, "Biasing Techniques for RF/IF Signal Processing"

Has the analog job market emerged into daylight? Certainly brighter times are upon us <a href="http://www.planetanalog.com/showArticle.jhtml?articleID=16401444">http://www.planetanalog.com/showArticle.jhtml?articleID=16401444</a>

- Consequently, we're seeing analog job requisitions in several key areas including WiFi (wireless LANs and Internet access), ultra wideband technology (UWB) and power management. Demand for designers with expertise in high-speed data conversion seems to be high across a variety of industries.

- At the height of communications funding bubble, designers of Serdes, CDR (clock-data recovery) and PLL (phase-locked loops) could count on receiving 10 job offers almost as soon as they flashed their resumes. While the comms bubble has burst, there remain a number of openings for designers with solid analog experience.

# Obituary Note on Jim Williams (Linear Technology ) – Most Popular Analog Design Expert !!!

Test equipment has to be more advanced than the circuits it tests. So learning the design of test equipment turned Jim into one of the best analog engineers in the world. He never confused description with understanding. When he would give seminars on how to design piezoelectric transformer lamp drivers, he pointed out that professors who fill the blackboard with math really don't know how a circuit works. Jim knew that the math can describe how a circuit works but understanding how it works was a much more fundamentally intuitive and poetic endeavor.

## **Analog Applications**

Motion/acceleration

Mechanical Force

**Sound Waves**

Electromagnetic Field

Temperature

Digital System, e.g.

- digital communication (DSL, GSM, ..., LTE)

- computer equipment

- multimedia (DVD, mp3, camera...)

- control application (e.g. automotive)

discrete sequence of numbers from a discrete set

Sense Organs

Sensors/Actuators

Time

Current/Voltage

Even digital signals on a transmission channel

Mixed Signal Electronics will be a bridge

## **Analog Applications**

- Sensor interface (P, Temp, accel, mass, gas, virus.....)

- Bio system

- Audio/video applications

- Digital storage media

- HDD, CD, DVD, BlueRay, Flash etc

- USB I/II/wireless USB, 1394 Std.

- Read/write channel

- Every digital system with high CK speed

- RF system

## **Analog Circuit Design Approaches**

**Approach – I:** quantum mechanics  $\rightarrow$  solid state physics  $\rightarrow$  semiconductor device physics  $\rightarrow$  device modelling  $\rightarrow$  design of circuits

**Approach – II:** semiconductor device as black box  $\rightarrow$  describe behavior of these black box in terms of terminal I and V  $\rightarrow$  design of circuits

Extremely tedious and time consuming

Extremely difficult to identify the cause of the problems

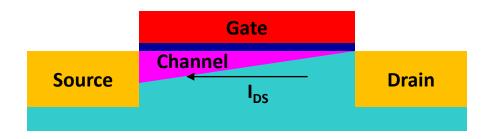

Channel

Drain

## ECE315 / ECE515

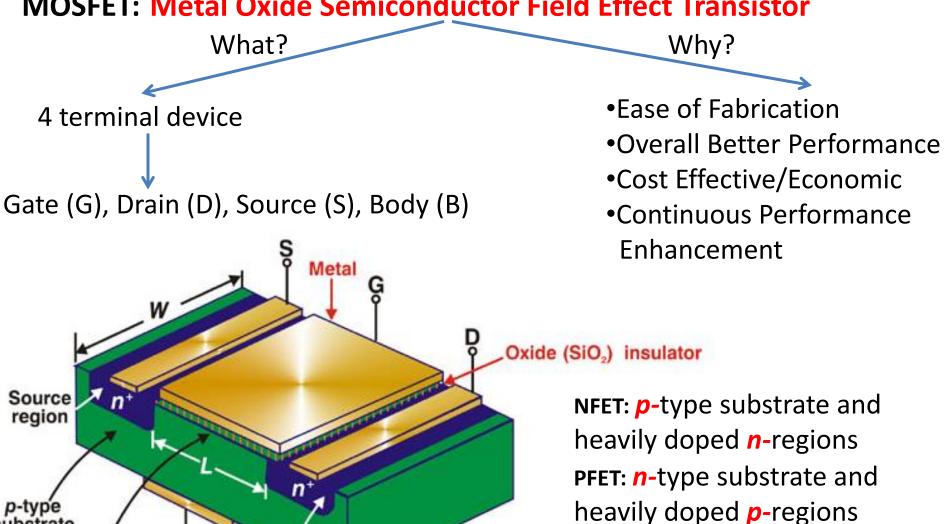

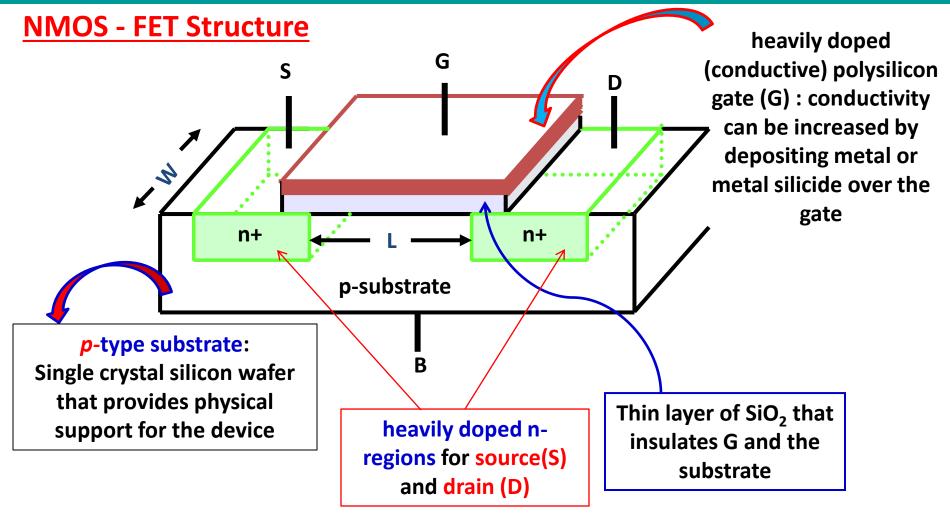

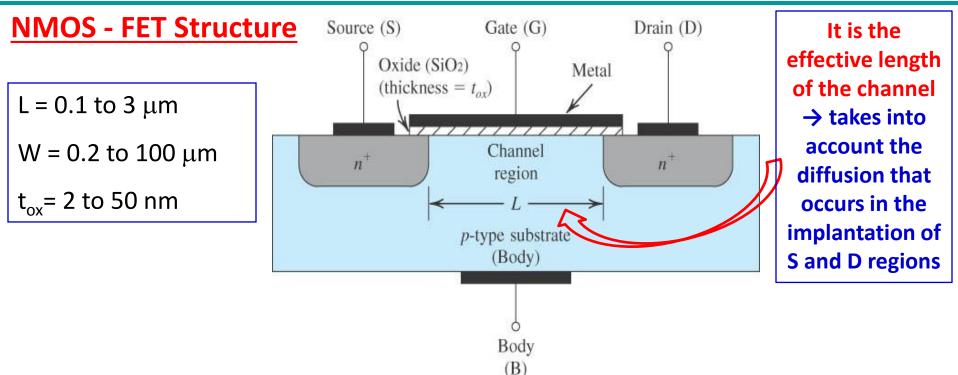

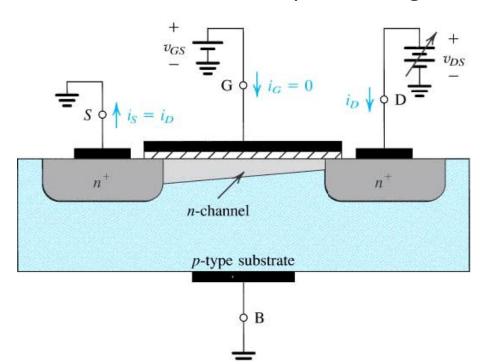

## **MOSFET: Metal Oxide Semiconductor Field Effect Transistor**

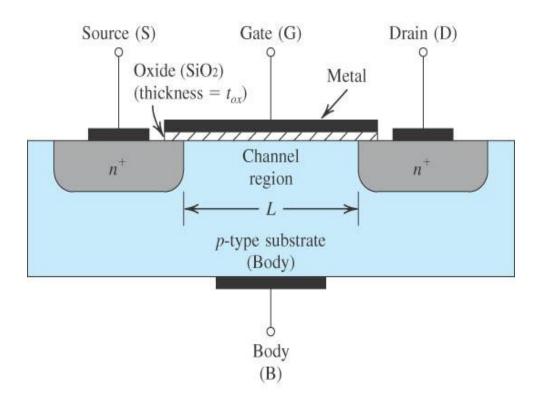

The dimension of the gate along the source-drain path is called the length, **L**, and the perpendicular to the length is called the width, **W**.

- Silicon Dioxide is essentially glass! Glass is a very good insulator—thus, no current can flow from the gate into the MOSFET device!

- Thus, the Silicon Dioxide layer is sandwiched between the metal Gate electrode and the p-type channel. It is these three materials that give the MOSFET its name—Metal (Gate electrode) Oxide (SiO<sub>2</sub>) Semiconductor (Substrate) FET.

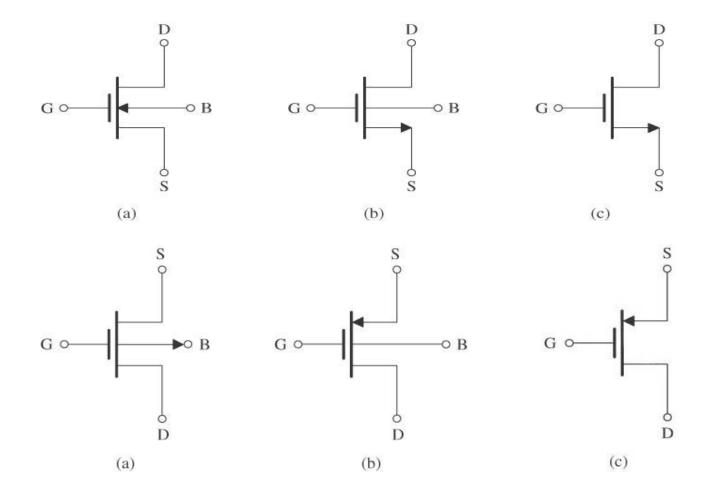

## **NMOS and PMOS Symbols**

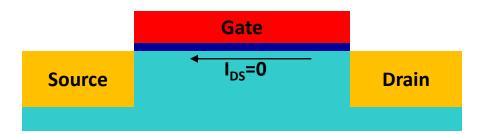

#### **Channel Creation for Current Flow**

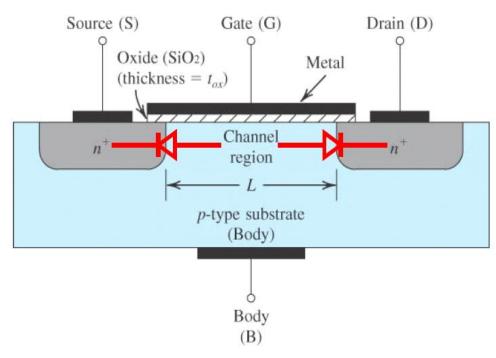

First glance at an NMOS device: it appears that no current can flow from the Drain to the Source (or vice versa) as we must contend with two p-n junctions!

- Current cannot flow **into** channel from the Drain, as this requires current flowing from an n-type (cathode) region into a p-type (anode) region.

- Similarly, current cannot flow into channel from the Source, as this

requires current flowing from an n-type (cathode) region into a p-type

(anode) region.

- Note that current **cannot** flow into (or out of) the channel from (into) the **gate**, as the SiO<sub>2</sub> layer is a very good **insulator**!

## **Channel Creation for Current Flow (contd.)**

Q: Pardon me, but this NMOS device does **not** appear to be particularly **useful.** I mean, what good is a device if **no** current can flow into it?

**A:** An NMOS device would indeed be useless **if** no current could flow from drain to source. However, we can **modify** the channel so that this current **can** indeed flow!

We must **induce a channel**—that is, create a thin layer of n-type channel connecting the source and drain!

## **Channel Creation for Current Flow (contd.)**

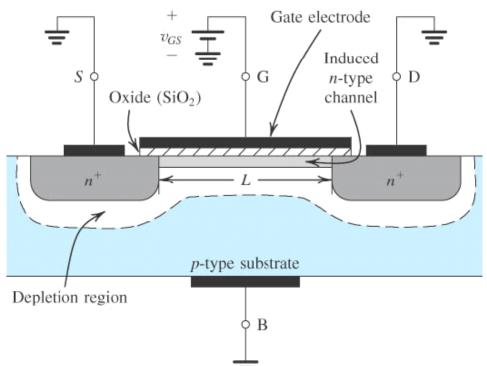

- For inducing a channel we place a positive voltage at the gate electrode.

- This creates an electric field within the p-type substrate, which pushes

the positively charged holes in the p-type substrate away from the gate

—a depletion region is formed in the Silicon under the gate!

The electric field under the gate will **repel** positively charged holes, but will **attract** negatively charged free electrons!

#### **Channel Creation for Current Flow (contd.)**

Q: I see! The minority carriers in the p-type substrate (i.e., **free electrons**) are attracted to the **gate** electrode!

A: True! But we also find that many of the free electrons attracted to the gate come from the **heavily doped** n+ wells called the source and drain.

- There is a Silicon Dioxide insulator separating the gate electrode and the Silicon substrate, so the free electrons attracted by the gate simply "pile up" at the top of the Silicon substrate, just under the SiO<sub>2</sub> layer.

- The result is an "inversion layer"—A thin layer in the p-type silicon where the majority carriers are actually free electrons!

#### **Channel Creation for Current Flow (contd.)**

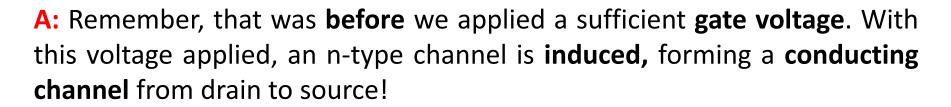

- This inversion layer forms n-type conducting channel connecting the n<sup>+</sup> drain to the n<sup>+</sup> source. By applying a positive voltage to the gate, we have induced a conducting channel!

- In other words, current flowing from drain to source no longer encounters any p-n junctions!

Q: So, will **any** positive gate voltage suffice for inducing a channel, **or** must this gate voltage be somehow sufficiently **large**?

A: The later. The gate voltage must be sufficiently large to create an inversion layer—it must be sufficiently large to induce a conducting channel.

$\rightarrow$  In fact, the voltage value must exceed some threshold (V<sub>T</sub>)  $\leftrightarrow$   $V_{GS} > V_{T}$

#### NMOS Qualitative Analysis – Enhancement Type

Assumption:  $V_{SB} = 0$

Case-I:  $0 \le V_{GS} < V_T$   $V_{GS} < V_T$

V<sub>GS</sub>: Gate-Source Voltage

V<sub>⊤</sub> : Threshold Voltage (lies between

0.3 to 0.5 V)

- The channel doesn't exist and therefore no current can flow between D and S

- The transistor is said to be in cut-off mode

## **Home Assignment # 0**

Why is V<sub>T</sub> always above 0 for an NMOS - FET? **Due by 12.08.2015**

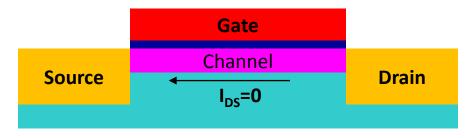

#### Case-II: $0 < V_{GS}$ , $V_{GS} \ge V_T$ and $V_{DS} = 0$

- The channel forms but still no current flows in the channel.

- The transistor in such a situation behaves as a  $V_{GS}$  controlled resistor  $\longleftrightarrow$  Increase in  $V_{GS}-V_T$  results in the increase of channel conductivity and hence reduction in the resistance value.

This process, of increasing the induced channel conductivity by increasing the excess gate voltage, is otherwise known as **channel enhancement**. This is where the **enhancement** MOSFET gets its name!

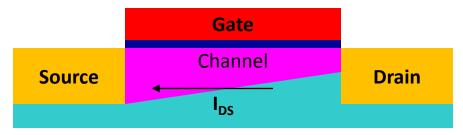

Case-III:  $0 < V_{GS}$ ,  $V_{GS} \ge V_T$  and  $0 < V_{DS} < V_{GS} - V_T$

$V_{DS} < V_{GS} - V_{T}$

- The transistor operates in triode mode or linear mode

- A current proportional to V<sub>DS</sub> starts to flow from D to S

- The transistor in this state behaves as a voltage controlled resistance

- Here it has been assumed that V<sub>GS</sub> V<sub>T</sub> is constant and V<sub>DS</sub> is varied

Q: Current! I thought current could **not** flow because of the two p-n junctions in the NMOS device!

## Case-III: $0 < V_{GS}$ , $V_{GS} \ge V_T$ and $0 < V_{DS} < V_{GS} - V_T$

- Recall that because of the SiO<sub>2</sub> layer, the gate current is **zero** (i.e.,  $I_G = 0$ ).

- Thus, all current entering the drain will exit the source. We therefore conclude that:  $I_D = I_S$ .

- As a result, we refer to the channel current for NMOS devices as simply the **drain current**  $I_D$ .

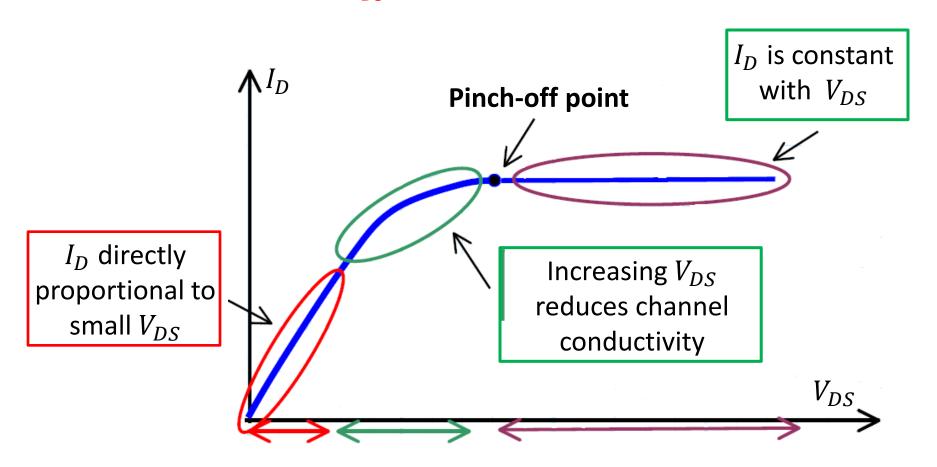

- For small  $V_{DS}$  (we will see how small later), the drain current will be **directly proportional** to the  $V_{DS}$ :

$I_D \propto V_{DS}$

• In other words, if  $V_{DS}$  is **zero**, the drain current  $I_D$  is **zero**. Or, if the voltage  $V_{DS}$  increases by 10%, the drain current will likewise increase by 10%. Note this is **just like a resistor**!

$$V = \frac{V}{R}$$

$$\therefore I \propto V$$

## Case-III: $0 < V_{GS}$ , $V_{GS} \ge V_T$ and $0 < V_{DS} < V_{GS} - V_T$

- In other words, we can (for small values of  $V_{DS}$ ), define a **channel resistance**  $R_{DS}$ :

- $R_{DS} = \frac{V_{DS}}{I_D}$

- Note that this resistance value depends on the conductivity of the induced channel—which in turn is dependent on the  $V_{GS}-V_T$ .

- In other words, the channel behaves like a **voltage controlled resistor** (provided  $V_{DS}$  is **small**):

$$R_{DS} = f(V_{GS} - V_T)$$

Q: Yawn! It is apparent that an NMOS transistor is so **simple** that virtually any intergalactic traveler should be able to design **resistor**—right? to understand it. It's just a **voltage controlled resistor**—right?

**A: WRONG!** Remember, channel resistance  $R_{DS}$  only has meaning if  $V_{DS}$  is small—and most often  $V_{DS}$  will **not** be small!

$\rightarrow$  As  $V_{DS}$  increases from our presumably small value, we find that strange things start to happen in our channel!

Recall that primarily, the **free-electrons** in our inversion layer (the induced channel) were attracted to the **gate** from the heavily doped **n+ drain** and **source**.

→ But the gate now has competition in attracting these free electrons!

- It was "easy" to attract free electrons to the gate when the gate voltage was much larger than both the drain and source voltage (i.e., when  $V_{GS} \gg V_{DS}$ ). But as the drain voltage increases, it begins to attract free electrons of its own!

- Recall that **positive current entering** the drain will actually consist mainly of **free electrons exiting** the drain! As a result, the **concentration** of free-electrons in inversion layer will begin to **decrease** in the vicinity of the **drain**.

In other words, increasing  $V_{DS}$  will result in decreasing channel conductivity!

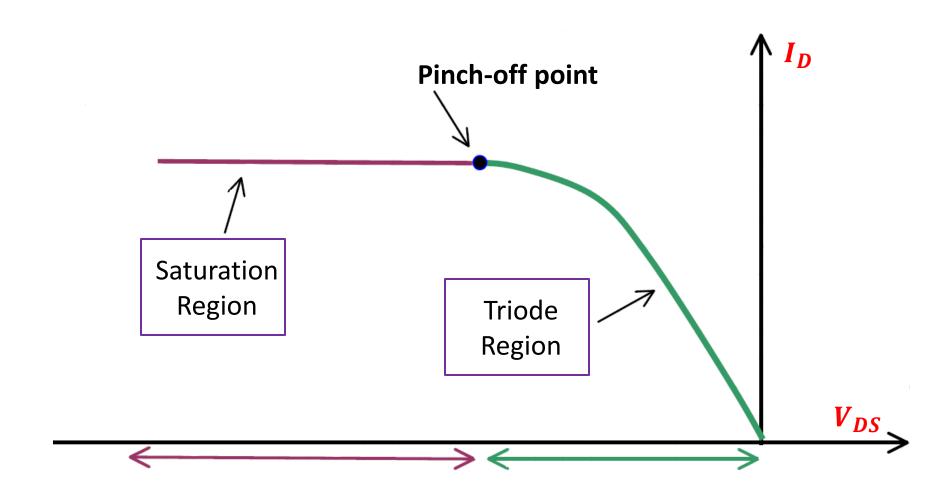

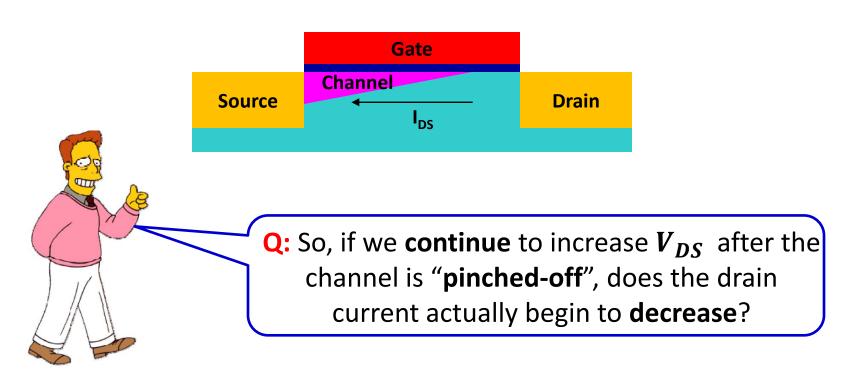

Case-IV: V<sub>GS</sub>≥V<sub>T</sub>, V<sub>DS</sub>=V<sub>D(SAT)</sub>

$$V_{DS} = V_{GS} - V_{T}$$

- The channel just reaches the drain

- The channel is reduced to zero inversion charge at the drain

- Drifting of electrons through the depletion region between the channel and drain begins

- This stage is known as pinch-off

At pinch-off: there is **no more** increase in drain current as  $V_{DS}$  increases.

Case-V:  $V_{GS} \ge V_{T,} V_{DS} \ge V_{D(SAT)}$

$$V_{DS} > V_{GS} - V_{T}$$

A: NO! An interesting thing happens when the channel is in pinch-off. As we further increase  $V_{DS}$ , the drain current  $I_D$  will remain unchanged (approximately)! That is, the drain current will be a constant (approximately) with respect to  $V_{DS}$ .

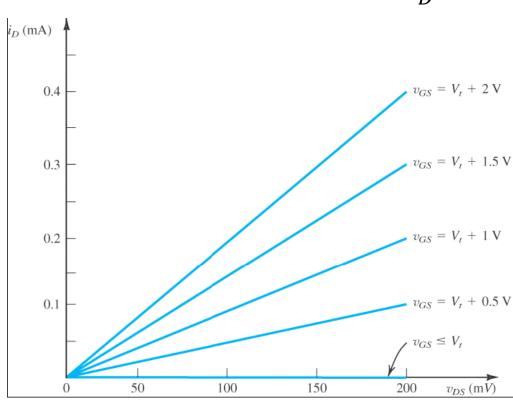

## **V**<sub>GS</sub>≥**V**<sub>T</sub>, Dependence on **V**<sub>DS</sub>:

#### **Summary:**

#### The NMOS characteristic curve has three distinct operation modes:

- **1. Cutoff** When  $V_{GS} V_T < 0$ , **no** channel is induced (no inversion layer is created), and so  $I_D = 0$ . We call this mode **CUTOFF**.

- **2. Triode** When an induced channel **is** present (i.e.,  $V_{GS} V_T > 0$ ), but the value of  $V_{DS}$  is **not** large enough to pinch-off this channel, the NMOS is said to be in **TRIODE** mode.

- **3. Saturation** When an induced channel **is** present (i.e.,  $V_{GS} V_T > 0$ ), and the value of  $V_{DS}$  **is** large enough to pinch-off this channel, the NMOS is said to be in **SATURATION** mode.

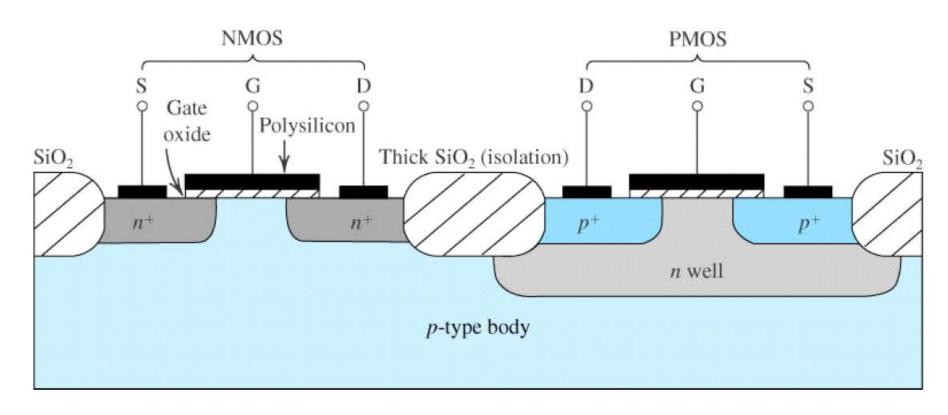

#### **PMOS and CMOS**

- In addition to an n-channel MOSFET device (i.e., NMOS), we can build p-channel MOSFET (i.e., PMOS) device.

- The structure of a PMOS device is essentially the same as an NMOS transistor, except that wherever there was n-type Silicon there is now p-type Silicon—and wherever there was p-type Silicon there is now n-type Silicon!

- Specifically, the PMOS channel is part of a n-type substrate lying between two heavily doped p+ wells beneath the source and drain electrodes.

- Generally speaking, a PMOS transistor is only constructed in **consort** with an NMOS transistor. This "pair" of NMOS and PMOS transistors is known as **Complementary MOS**FETs—**CMOS** for short!

#### PMOS and CMOS (contd.)

The operation of a PMOS transistor is in many ways **similar** to that of the NMOS device, but in many ways they are also **quite different!**

#### For a **PMOS** device:

- To create an inversion layer in the n-type substrate, we must attract holes

to the gate → as a result, a p-type channel will be induced, connecting

the p+ wells at the drain and the source.

- However, to attract **holes** toward the gate, the voltage  $V_{GS}$  must be sufficiently **negative**! For PMOS, the threshold voltage  $V_T$  is a **negative** value, so that a channel is induced only if  $V_{GS} < V_T$  (i.e.,  $V_{GS}$  is more **negative** than  $V_T$ )  $\rightarrow$  a channel is induced in a **PMOS** device **only** if  $V_{GS} V_T$  is **negative** (i.e.,  $V_{GS} V_T < 0$ ).

- Similarly, we typically get current to flow through this channel by making the voltage  $V_{DS}$  negative. If we make the voltage  $V_{DS}$  sufficiently negative, the p-type induced channel will pinch-off.

- Note that when  $V_{DS}$  is **negative**, the drain current will flow **from** the PMOS **source**, **to** the PMOS **drain** (i.e., exactly **opposite** that of the NMOS device with a positive  $V_{DS}$ ).

PMOS:  $I_D vs V_{DS}$  curve: