Date: 17.09.2015

## **Lecture – 11**

- Non-idealities in Current Mirror

- Cascode Current Mirror

- Current Mirror Configurations

- Examples

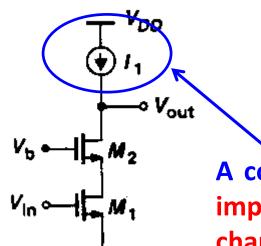

### **Cascode Amplifier with Current Source Load**

We know the gain of Cascode stage is given by:

$$\Rightarrow A_{v} \approx -\frac{g_{m1}(g_{m2} + g_{mb2})r_{o1}r_{o2}}{\left[R_{D} + r_{o1} + r_{o2} + (g_{m2} + g_{mb2})r_{o1}r_{o2}\right]}R_{D}$$

A constant current source possesses very high output impedance ( $R_D \rightarrow \infty$ ), therefore the gain equation changes to:

It is apparent that the maximum small-signal voltage gain is the multiplication of gains from CS and CG stages → definitely a big plus!

$$R_{out} \approx (g_{m2} + g_{mb2}) r_{o2} r_{o1}$$

### **Cascode – Amplifier (contd.)**

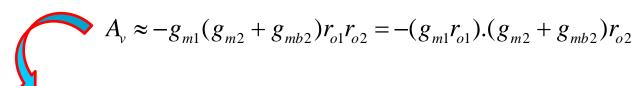

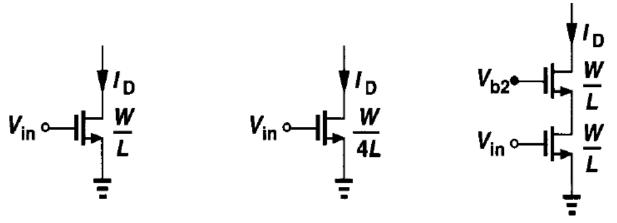

### Discussion with respect to alteration in dimension

What happens if <u>Length (L)</u> of the main device is quadrupled while the <u>Width</u> (W) remains same?

Cascode more suited for noise applications

### **Cascode – Amplifier (contd.)**

#### Discussion with respect to alteration in dimension

$$(V_{GS} - V_{TH})^2 = \frac{2I_D}{\mu_n C_{ox} \left(\frac{W}{L}\right)}$$

Quadruppling of **Length (L)** while keeping the Width (W) results in doubling of overdrive voltage

For **identical devices**, cascode also exhibits doubling of overdrive voltage

### **Shielding Property of Cascode**

Cascode amplifier and Cascode current source → could be used in applications where the output varies drastically due to any reason!

$\rightarrow$  This variation doesn't affect the subsequent sections greatly  $\rightarrow$ shielding property of Cascode

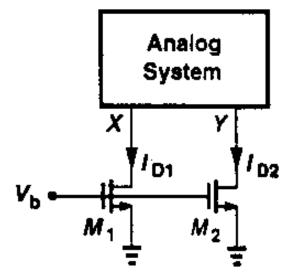

**Example:** Two identical NFETs are used to generate constant current sources. However, due to internal circuitry of the system, V<sub>x</sub> is higher than  $V_{v}$  by  $\Delta V$ .

Q: determine the resulting difference between I<sub>D1</sub> and  $I_{D2}$  if  $\lambda \neq 0$

$$I_{D1} = \frac{1}{2} \mu_n C_{ox} (V_b - V_T)^2 (1 + \lambda V_X)$$

$$I_{D2} = \frac{1}{2} \mu_n C_{ox} (V_b - V_T)^2 (1 + \lambda V_Y)$$

$$I_{D1} - I_{D2} = \frac{1}{2} \mu_n C_{ox} (V_b - V_T)^2 (\lambda \Delta V)$$

$$I_{D1} - I_{D2} = \frac{1}{2} \mu_n C_{ox} (V_b - V_T)^2 (\lambda \Delta V)$$

### **Shielding Property of Cascode (contd.)**

Q: Add Cascode devices to M1 and M2 and then check the difference between  $I_{D1}$  and  $I_{D2}$  if  $\lambda \neq 0$

This is a large value and thus the Cascode structure gives smaller variation → perfect example of Shielding property!!!

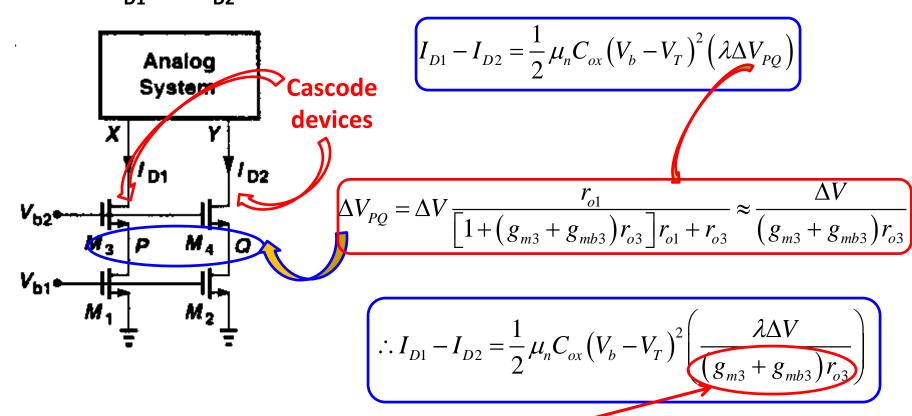

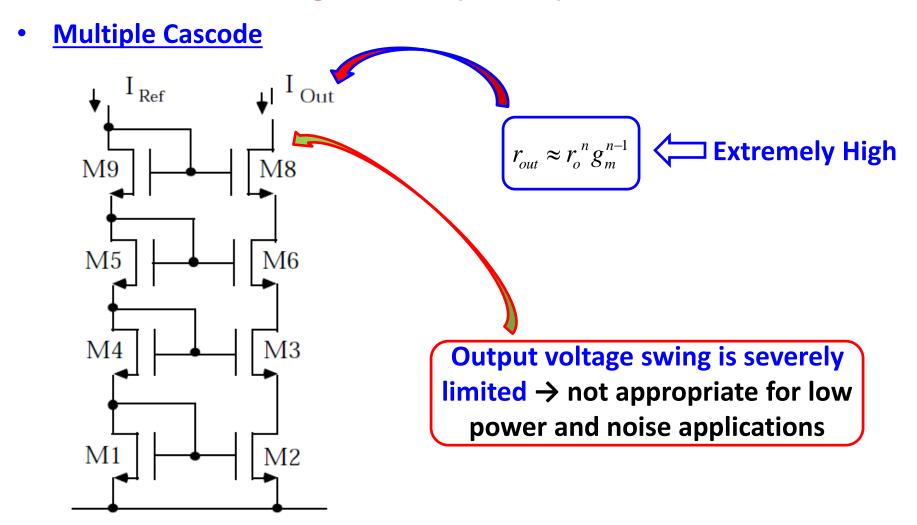

### **Triple Cascode**

Cascoding can be extended to three or more devices to achieve higher output impedance

### **Folded Cascode**

**Self Study**

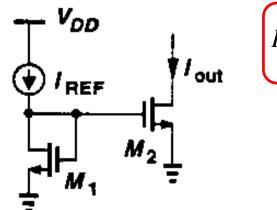

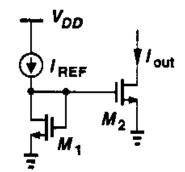

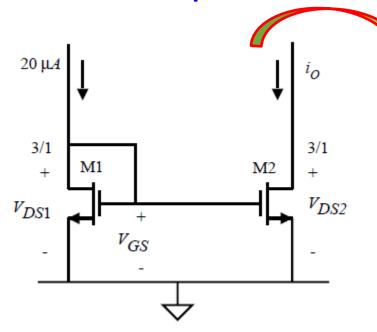

#### **Current Mirror**

Now let us take the generic equations for the following current mirror:

$$I_{REF} = \frac{1}{2} \mu_{n1} C_{ox1} \left( \frac{W}{L} \right)_{1} (V_{GS1} - V_{T1})^{2}$$

$$I_{out} = \frac{1}{2} \mu_{n2} C_{ox2} \left(\frac{W}{L}\right)_2 (V_{GS2} - V_{T2})^2$$

Even if these transistors are identical and have been fabricated on the same chip [thus practically possessing similar parameters such as  $V_T$ ,  $\mu_n$ ,  $C_{ox}$ ], there are three effects that causes current mirror to be different from ideal situation

These effects are: (a) Channel Length Modulation, (b) V<sub>T</sub> offset between the two transistors, (c) Imperfect Geometrical Matching

### **Current Mirror (contd.)**

#### **Channel Length Modulation Effect**

Assuming all other aspects of the transistor are ideal and the <u>ratio</u> of aspect ratios of both the transistors are unity then:

### **Current Mirror (contd.)**

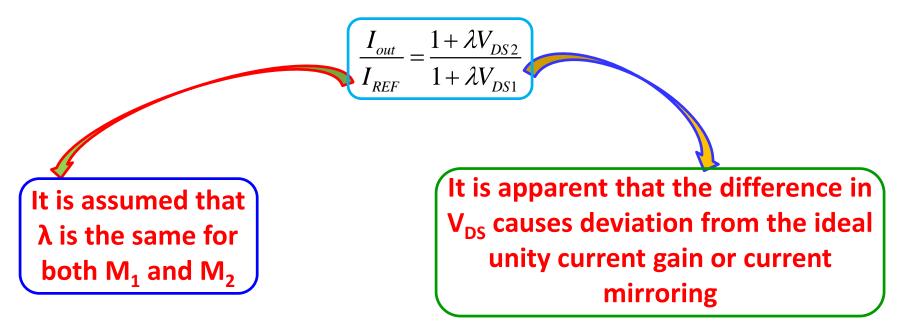

**Channel Length Modulation Effect (contd.)**

Significant Ratio Error can exist when mirror transistors do not have the same V<sub>DS</sub>

For a given V<sub>DS</sub>, the ratio improves with decreasing λ (i.e, increasing output resistance)

Therefore, a good current mirror should have identical V<sub>DS</sub> and high output resistance

Current Ratio Error vs  $(V_{DS2} - V_{DS1})$  for different values of  $\lambda$

### **Current Mirror (contd.)**

**Channel Length Modulation Effect (contd.)**

- Therefore, the apparent solution seems the use of long channel device

- however this also requires increase in width → results in problems for area and power constraint designs

- furthermore, increase in width also increases the output capacitance

high frequency performance suffers

- short channel devices are commonplace and therefore this solution is not appropriate

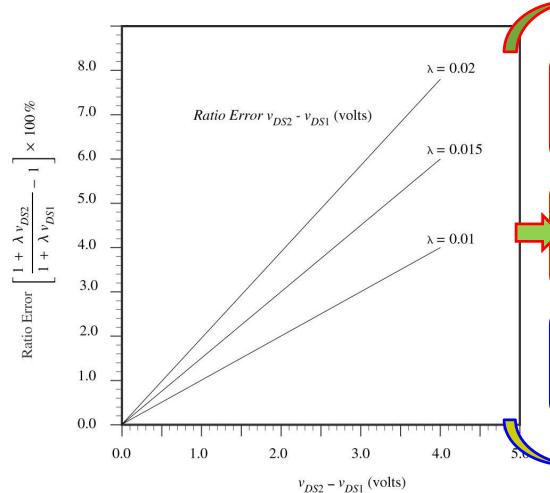

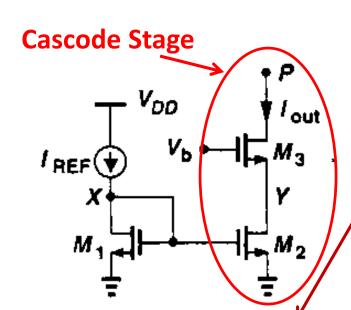

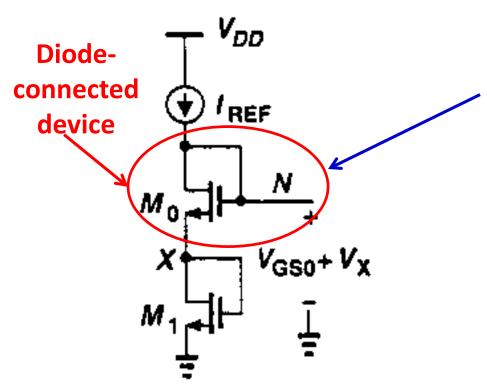

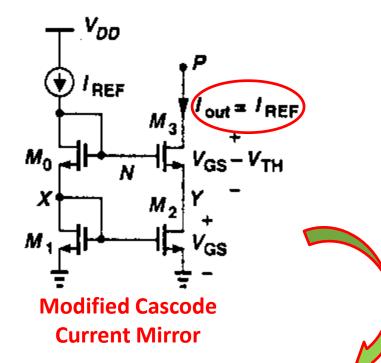

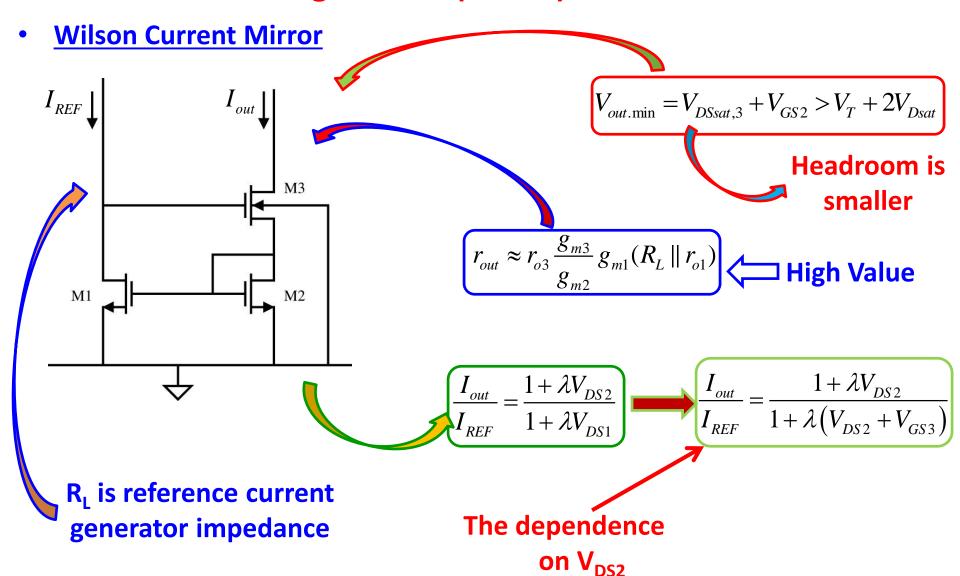

#### **Cascode Current Mirror**

In order to overcome the error due to channel length modulation, instead of a simple two transistor "current mirror" it is recommended to use "cascode current mirror"

- In this architecture, small changes in potential at node-P does not have any effect on the potential at node-Y -> shielding property of Cascode

- Through some technique make  $V_Y = V_X$   $\rightarrow$  then the effect of channel length modulation is insignificant as the mirror equation becomes:

$$\Delta V_Y = \Delta V_P / [(g_{m3} + g_{mb3})r_{o3}]$$

Once again only dependent on the scaling of devices

$$I_{out} = I_{REF} \frac{(W/L)_2}{(W/L)_1}$$

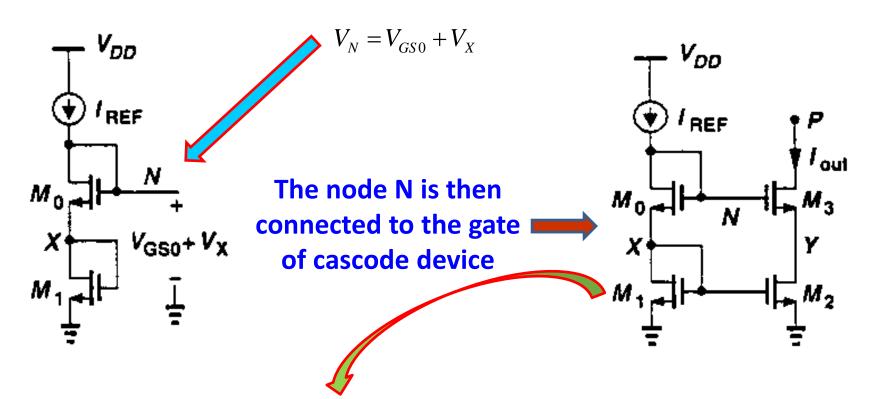

### **Cascode Current Mirror (contd.)**

- How do we generate the condition: V<sub>Y</sub> = V<sub>X</sub>

- For this to happen, we must guarantee  $V_b V_{GS3} = V_X \rightarrow It$  means one gate-source voltage should be added to achieve this  $\rightarrow$  this is easily achieved by placing a diode-connected device  $M_0$  in series with  $M_1$

Addition of this device will ensure fulfillment of:  $V_h - V_{GS3} = V_x$

Then proper choice of dimensions of M<sub>0</sub> and M<sub>3</sub> yields V<sub>GS0</sub> = V<sub>GS3</sub>

### **Cascode Current Mirror (contd.)**

$$V_{GS0} + V_X + V_{GS1} = V_{GS3} + V_Y + V_{GS2}$$

$$\therefore V_{GS0} + V_X = V_{GS3} + V_Y$$

proper choice of dimensions of M<sub>0</sub> and M<sub>3</sub> yields V<sub>GS0</sub> = V<sub>GS3</sub>

### **Cascode Current Mirror (contd.)**

- Thus appropriate choices of dimensions of M<sub>0</sub> and M<sub>3</sub> gives: V<sub>GS0</sub> = V<sub>GS3</sub>

- For this to happen:

$$\frac{(W/L)_3}{(W/L)_0} = \frac{(W/L)_2}{(W/L)_1}$$

- Once  $V_{GSO} = V_{GS3}$ , we get:  $V_X = V_Y$

- $V_X = V_Y$  leads to the condition:  $V_{DS1} = V_{DS2} \rightarrow$  transforms the mirror equation:

$I_{out} = I_{REF} \frac{(W/L)_2}{(W/L)_1}$ exist body effect in transistors  $M_0$  and  $M_3$

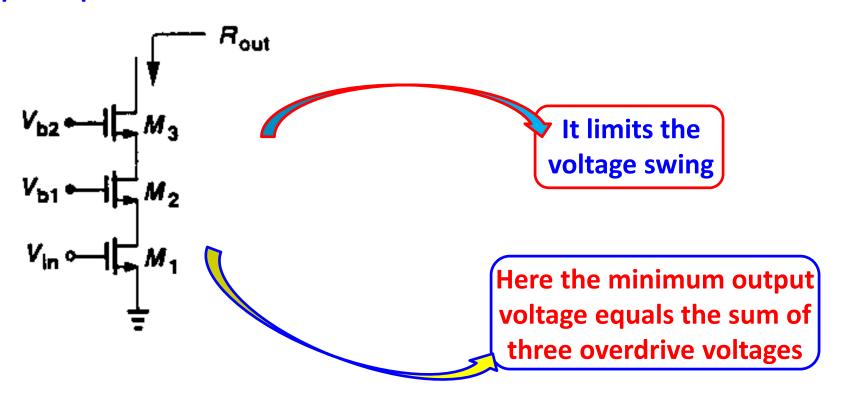

Cascode configuration improves the accuracy of current copying capability → but what is the major drawback?

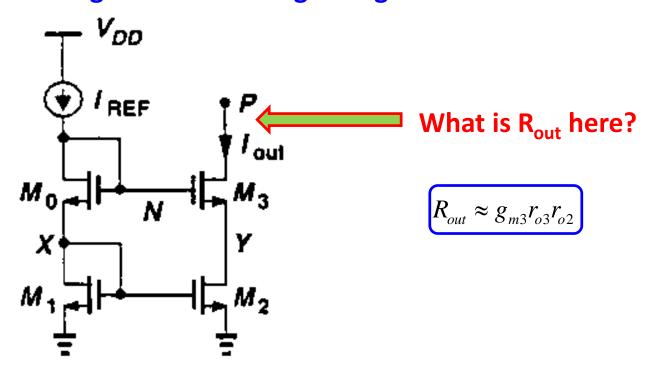

### **Cascode Current Mirror (contd.)**

- As the cascode current mirror provides a constant current source, it should also possess very high output impedance

- Consider once again the following configuration:

### **Cascode Current Mirror (contd.)**

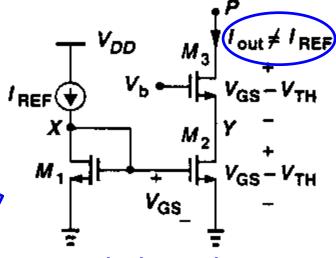

**Accuracy and Voltage Swing Trade-off**

Standard Cascode

Current Mirror

- V<sub>b</sub> is chosen to allow minimum V<sub>p</sub>

- Problem: V<sub>X</sub> ≠ V<sub>Y</sub>

- | out ≠ | ref

- V<sub>b</sub> is chosen to allow V<sub>X</sub>=V<sub>Y</sub>

- V<sub>p</sub> is not minimum

- However, I<sub>out</sub> = I<sub>ref</sub>

### **Current Mirror (contd.)**

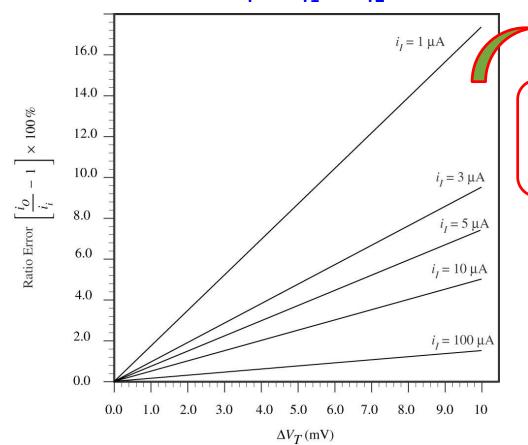

#### **Threshold Offset Effect**

- The offset between the threshold voltage of two transistors also causes problems in the optimal operation of current mirror

- The threshold offset is typically less than 10mV for identical transistors

→ even this small offset causes substantial error!!!

- Let us now consider a current mirror configuration where both have the same V<sub>DS</sub> and all other aspects of the transistors are equal except V<sub>T</sub>.

The expression simplifies to:

$$\frac{I_{out}}{I_{REF}} = \left(\frac{V_{GS} - V_{T2}}{V_{GS} - V_{T1}}\right)^{2}$$

### **Current Mirror (contd.)**

#### **Threshold Offset Effect (contd.)**

• The plot of ratio error between ideal and imperfect current mirroring as a function of  $\Delta V_T = V_{T1} - V_{T2}$  results into:

Clearly identifies that better current mirroring is obtained for higher currents

Its due to the fact that  $V_{GS}$  is higher for higher currents  $\rightarrow$  ensures that  $\Delta V_{T}$  is a smaller percentage of  $V_{GS}$

### **Current Mirror (contd.)**

### **Threshold Offset Effect (contd.)**

- Sometimes it may happen that the factor  $\mu_n C_{ox}$  (let us call it K') is also mismatched alongwith the offset in the threshold.

- The current mirror equation then transforms to:

$$\frac{I_{out}}{I_{REF}} = \frac{K_{2}^{'}(V_{GS} - V_{T2})^{2}}{K_{1}^{'}(V_{GS} - V_{T1})^{2}}$$

In this case its assumed that the aspect ratio is identical (considering that its designer driven!).

Let us define:

$$\Delta K' = K_2' - K_1' \qquad K' = \frac{1}{2} (K_2' + K_1') \qquad V_T = \frac{1}{2} (V_{T1} + V_{T2})$$

Then:

$$K_{1}^{'} = K^{'} - 0.5\Delta K^{'}$$

$K_{2}^{'} = K^{'} + 0.5\Delta K^{'}$   $V_{T1} = V_{T} - 0.5\Delta V_{T}$   $V_{T2} = V_{T} + 0.5\Delta V_{T}$

### **Current Mirror (contd.)**

### **Threshold Offset Effect (contd.)**

Let us substitute the mirror equation using these assumed parameters:

$$\frac{I_{out}}{I_{REF}} = \frac{\left(K' + 0.5\Delta K'\right) (V_{GS} - V_T - 0.5\Delta V_T)^2}{\left(K' - 0.5\Delta K'\right) (V_{GS} - V_T + 0.5\Delta V_T)^2}$$

Factor out K' and (V<sub>GS</sub> – V<sub>T</sub>) to get:

$$\frac{I_{out}}{I_{REF}} = \frac{\left(1 + \frac{\Delta K}{2K}\right) \left(1 - \frac{\Delta V_T}{2(V_{GS} - V_T)}\right)^2}{\left(1 - \frac{\Delta K}{2K}\right) \left(1 + \frac{\Delta V_T}{2(V_{GS} - V_T)}\right)^2}$$

Assuming these quantities to be small, we get:

$$\left(\frac{I_{out}}{I_{REF}} = \left(1 + \frac{\Delta K'}{2K'}\right) \left(1 + \frac{\Delta K'}{2K'}\right) \left(1 - \frac{\Delta V_T}{2(V_{GS} - V_T)}\right)^2 \left(1 - \frac{\Delta V_T}{2(V_{GS} - V_T)}\right)^2\right)$$

### **Current Mirror (contd.)**

### **Threshold Offset Effect (contd.)**

• Retaining only the first order products gives:

$$\frac{I_{out}}{I_{REF}} \cong 1 + \frac{\Delta K'}{K'} - \frac{2\Delta V_T}{V_{GS} - V_T}$$

If the percentage change of K' and V<sub>T</sub> are known apriori, then this expression can predict the worst-case error in the current mirroring capability of the current mirror

For example, if:

$$\frac{\Delta K'}{K'} = \pm 5\%$$

and:

$$\frac{\Delta V_T}{V_{GS} - V_T} = \pm 10\%$$

then:

$$\frac{I_{out}}{I_{REF}} \cong 1 \pm 0.05 \pm (-0.2) = 1 \pm (-0.15)$$

In this example, the maximum error amounts to 15% provided the tolerances in K' and  $V_T$  are correlated

### **Current Mirror (contd.)**

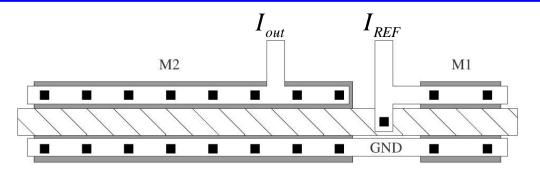

### **Mismatch in Aspect Ratio**

- mismatches are commonly present even in identical transistors on the same die ← W and L are often mismatched due to mask, photolithography, and diffusion variations → this can be significant even for two transistors placed side by side

- One way to overcome these effects is to make transistors much larger than these variations  $\rightarrow$  e.g., for transistors of identical size with W and L greater than  $10\mu m$ , the errors due to the mismatched aspect ratio will be insignificant  $\leftarrow$  when compared to errors contributed by offset  $V_T$  and Channel Length Modulation

- However, many applications (for high current gain applications!) require aspect ratio of transistor (M₂) to be much larger than the aspect ratio of the reference transistor (M₁) ← necessitates creativity in layout techniques!!!

### **Current Mirror (contd.)**

#### Mismatch in Aspect Ratio (contd.)

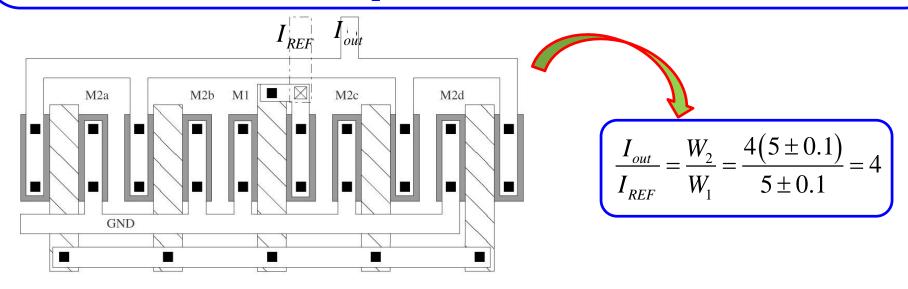

Example: we see layout of one-to-four current amplifier below. Its assumed that the lengths are identical ( $L_1 = L_2$ ). Find the ratio error if:

$$W_1 = 5 \pm 0.1 \mu m$$

$W_2 = 20 \pm 0.1 \mu m$

$$\frac{I_{out}}{I_{REF}} = \frac{W_2}{W_1} = \frac{20 \pm 0.1}{5 \pm 0.1} = 4 \left( \frac{1 \pm (0.1/20)}{1 \pm (0.1/5)} \right) \approx 4 \left( 1 \pm \frac{0.1}{20} \right) \left( 1 - \frac{\pm 0.1}{5} \right)$$

$$\Rightarrow \frac{I_{out}}{I_{REF}} = 4\left(1 \pm \frac{0.1}{20} - \frac{\pm 0.4}{20}\right) \approx 4\left(1 - \left(\pm 0.06\right)\right)$$

$\Rightarrow \frac{I_{out}}{I_{REF}} = 4 \left( 1 \pm \frac{0.1}{20} - \frac{\pm 0.4}{20} \right) \approx 4 \left( 1 - \left( \pm 0.06 \right) \right)$  It is assumed that variations would have the same sign. In this case it is apparent that the ratio error is 1.5% of the desired current ratio

### **Current Mirror (contd.)**

**Mismatch in Aspect Ratio (contd.)**

- For large W, it's a good strategy to have W not much larger than L and to put equal transistors in parallel.

- A solution to this problem is to use appropriate layout technique. For example, use four duplicates of transistor M<sub>1</sub> to achieve one-to-four ratio.

This way the tolerance on W<sub>2</sub> is multiplied by the nominal current gain.

Here its assumed that  $\Delta W$  should be the same for all the transistors

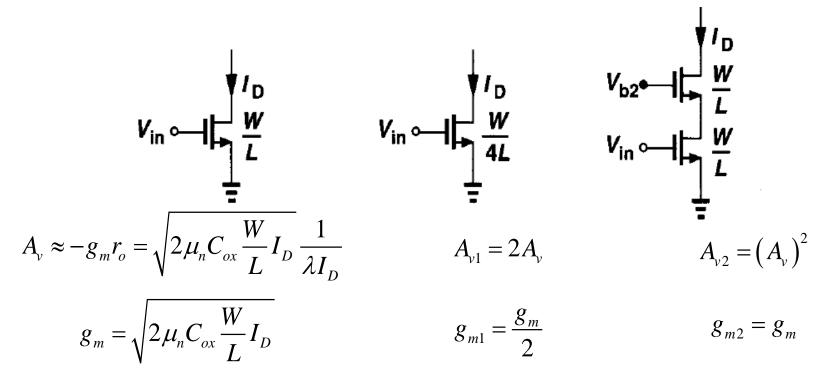

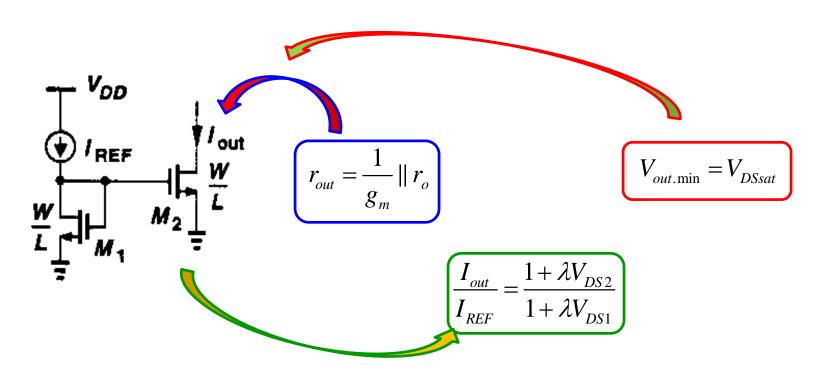

### **Current Mirror Configurations**

- It is a common practice to design current mirror circuits for high output impedance [for achieving near ideal current source!]

- No less important is the voltage headroom [specially for low voltage applications!!!]

### **Current Mirror Configurations (contd.)**

### **Current Mirror Configurations (contd.)**

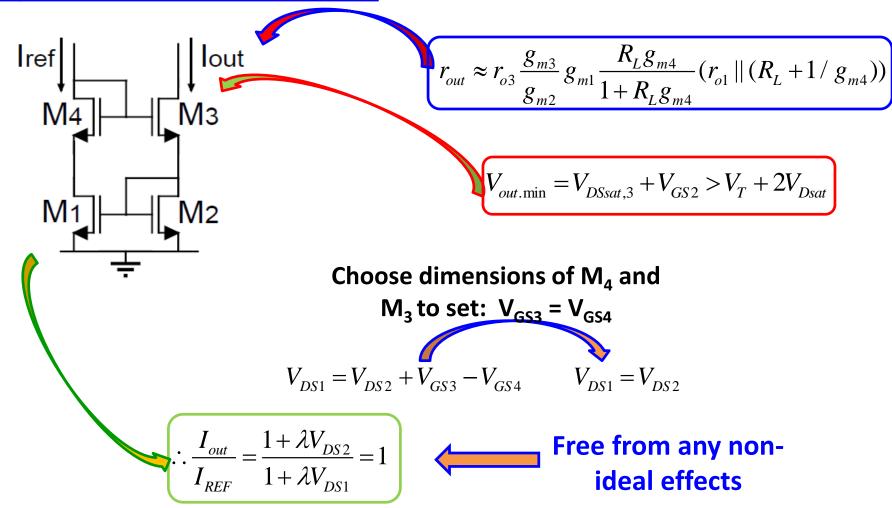

Improved Wilson Current Mirror

### **Current Mirror Configurations (contd.)**

## **Current Mirror Configurations (contd.)**

| Configurations Simple | Current Ratio $\frac{1 + \lambda V_{DS2}}{1 + \lambda V_{DS1}}$ | Output Swing $V_{DSsat}$                                   | Output Impedance $\frac{1}{g_m}    r_o$ |

|-----------------------|-----------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------|

| Cascode               | 1                                                               | $2V_{\scriptscriptstyle DSsat} + V_{\scriptscriptstyle T}$ | $r_o^2.g_m$                             |

| Triple Cascode        | 1                                                               | $3V_{DSsat} + 2V_{T}$                                      | $r_o^3.g_m^2$                           |

| Wilson                | $\frac{1 + \lambda V_{DS2}}{1 + \lambda V_{DS1}}$               | $2V_{DSsat} + V_{T}$                                       | $r_o^2.g_m$                             |

| Improved<br>Wilson    | 1                                                               | $2V_{DSsat} + V_T$                                         | $r_o^2 \cdot g_m$                       |

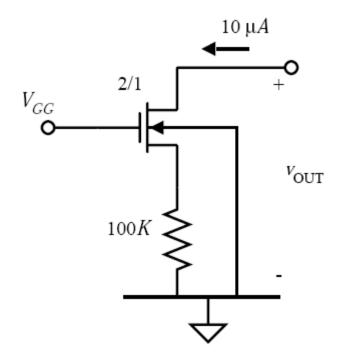

### **Example-1**

Following figure illustrates a source-degenerated current source. Calculate the output resistance at the given bias current by using the following model parameter:  $\mu_n C_{ox} = 110~\mu\text{A/V}^2,~\lambda = 0.04~(\text{L=1}~\mu\text{m})~\text{or}~0.01~(\text{L=2}\mu\text{m})~\text{/V},~2 | \varphi_F| = 0.7~,~\Upsilon = 0.4~\text{V}^{1/2}$

### Example-1 (contd.)

#### The dc terminal conditions are:

$$I_D = 10 \mu A$$

$$V_S = I_D * R = 10 * 10^{-6} \times 100 * 10^3 = 1V$$

$$V_{SB} = V_{S}$$

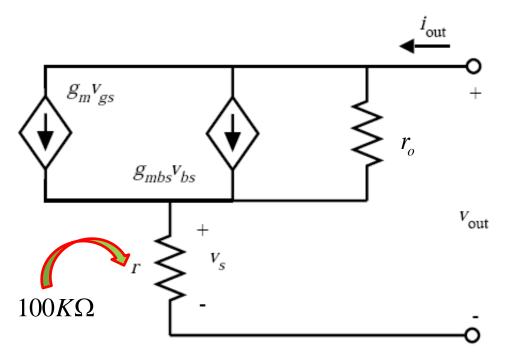

### Now the small signal model of the circuit is:

### **Simplification gives:**

$$r_{out} = \frac{v_{out}}{i_{out}} = r + r_{out} + \left[ \left( g_m + g_{mbs} \right) r_o \right] r$$

## Can be approximated to:

$$r_{out} = g_m r_o r$$

### Example-1 (contd.)

### The device parameters can be computed as:

$$g_m = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_D}$$

$g_m = \sqrt{2 \times 110 \times 10^{-6} \times \frac{2}{2} \times 10 \times 10^{-6}}$   $g_m = 66.3 \times 10^{-6}$

$$g_{mbs} = g \frac{\gamma}{2(2|\phi_F| + V_{SB})^{1/2}} \implies g_{mbs} = 66.3 * 10^{-6} \frac{0.4}{2(0.7 + 1)^{1/2}} \implies \therefore g_{mbs} = 10.17 \times 10^{-6}$$

$$r_o = \frac{1}{\lambda I_D}$$

$\therefore r_o = 2.5 \times 10^6 \Omega$

Thus:

$$r_{out} = 100*10^3 + 2.5*10^6 + \left[ \left( 66.6*10^{-6} + 10.17*10^{-6} \right) 2.5*10^6 \right] 100*10^3 = 21.7*10^6 \Omega$$

The approximated:  $r_{out} = 66.6*10^{-6} \times 2.5*10^{6} \times 100*10^{3} = 16.65*10^{6} \Omega$

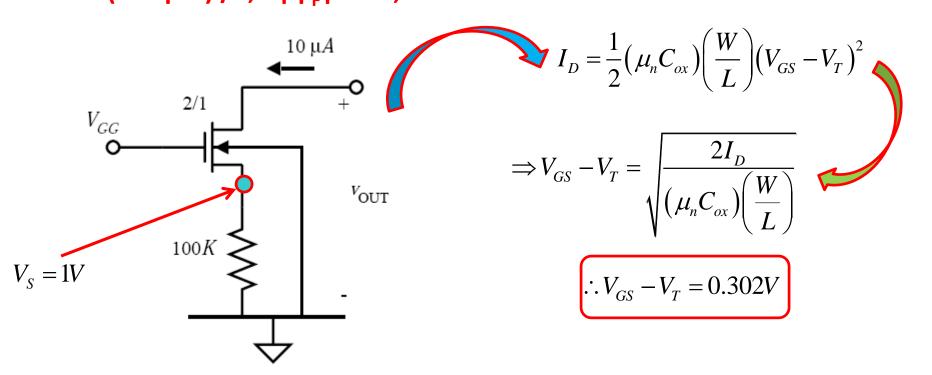

### **Example-2**

Calculate the minimum output voltage required to keep device in saturation in example-1. The model parameters:  $\mu_n C_{ox} = 110~\mu A/V^2$ ,  $\lambda = 0.04~(L=1~\mu m)$  or 0.01 (L=  $2\mu m$ ) /V,  $2|\varphi_E|=0.7$ ,  $\Upsilon=0.4~V^{1/2}$

$$V_D(\min) = V_S + (V_{GS} - V_T)(\min) = 1 + 0.302 = 1.302V$$

### **Example-3**

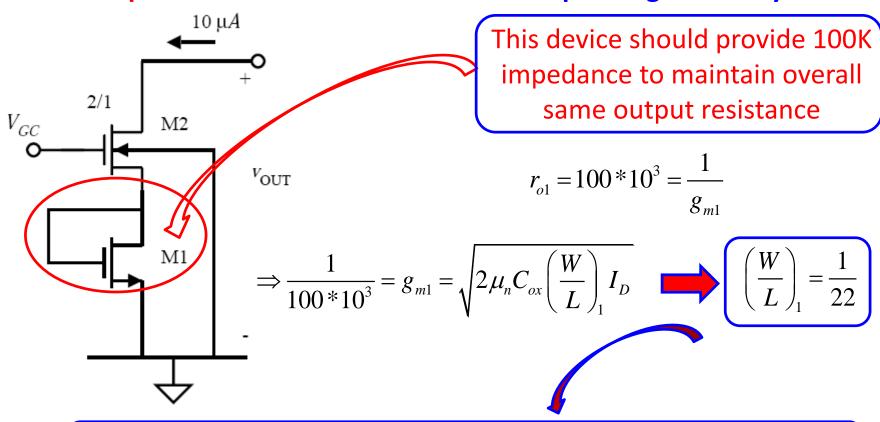

Using the Cascode circuit shown below, design the W/L of M1 to achieve the same output resistance as the circuit in example-1. Ignore body effect.

Note that the terminal conditions of M2 must change to support the large gate voltage required for M1

### **Example-4**

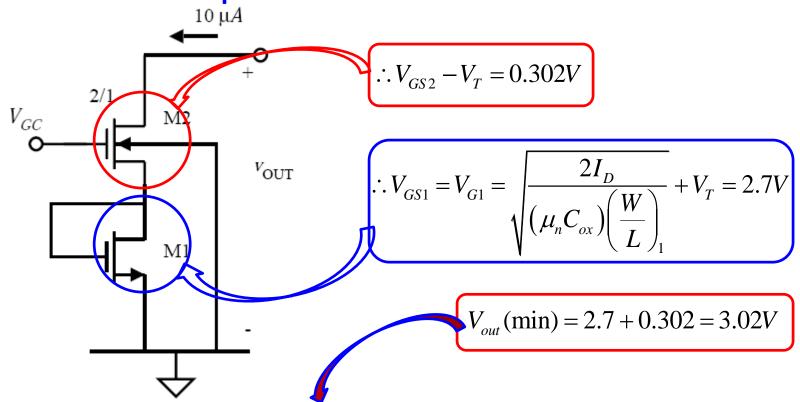

Now calculate the minimum output voltage required to keep the devices in saturation in example-3.

The minimum output voltage for circuit in example-1 is lower than the minimum output voltage for circuit in example-3, therefore is a better choice for low voltage applications

### **Example-5**

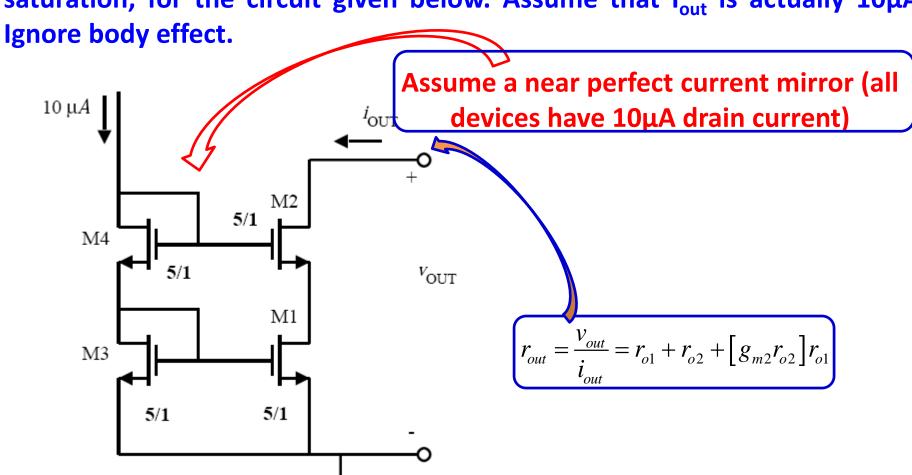

Calculate the output resistance, while maintaining all the devices in saturation, for the circuit given below. Assume that  $I_{out}$  is actually 10µA.

### Example-5 (contd.)

$$r_{out} = \frac{v_{out}}{i_{out}} = r_{o1} + r_{o2} + [g_{m2}r_{o2}]r_{o1}$$

$$r_{o1} = r_{o2} = \frac{1}{\lambda I_D} = 2.5 * 10^6 \Omega$$

$$g_{m2} = \sqrt{2(\mu_n C_{ox}) \left(\frac{W}{L}\right)_2 I_D} = 104.9 * 10^{-6}$$

$$\therefore r_{out} = 2.5 * 10^6 + 2.5 * 10^6 + \left[104.9 * 10^{-6} \times 2.5 * 10^6\right] 2.5 * 10^6 \approx 661 * 10^6 \Omega$$

### **Example-6**

Consider the simple current mirror given below.

Over process, the absolute variations of physical parameters are as:

Width Variation +/- 5% Length Variation +/- 5%  $V_T$  variation +/- 5%  $\mu_n C_{ox}$  Variation +/- 5%

Assuming that the drain voltages are identical, what is the minimum and maximum output current measured over the process variations given above. The model parameters:  $\mu_n C_{ox} = 110 \ \mu\text{A/V}^2$ ,  $\lambda = 0.04 \ (\text{L=1} \ \mu\text{m})$  or 0.01 (L= 2 $\mu$ m) /V, 2 |  $\varphi_F$  |=0.7 , Y=0.4 V<sup>1/2</sup>

### Example-6 (contd.)

#### We know:

$$I_{D} = \frac{1}{2} (U_{n}C_{ox}) \frac{W}{L} (V_{GS} - V_{T})^{2}$$

$$\Rightarrow V_{GS} = \sqrt{\frac{2I_D}{K\left(\frac{W}{L}\right)}} + V_T$$

• Assuming equal  $V_{GS}$  for both the transistors, we can express  $i_o = \frac{1}{2} K_2 \left( \frac{W}{L} \right)_2 \sqrt{\frac{2 \times I_{\text{Re}\,f}}{K_1 \left( \frac{W}{L} \right)}} + V_{T1} - V_{T2}$  the output current as:

We can deduce from this equation that the minimum and maximum of output current will happen under respective following conditions.

|                      | K <sub>1</sub> | K <sub>2</sub> | (W/L) <sub>1</sub> | (W/L) <sub>2</sub> | V <sub>T1</sub> | V <sub>T2</sub> |

|----------------------|----------------|----------------|--------------------|--------------------|-----------------|-----------------|

| i <sub>o</sub> (min) | Max            | Min            | Max                | Min                | Min             | Max             |

| i <sub>o</sub> (max) | Min            | Max            | Min                | Max                | Max             | Min             |